Straipsnis tikrai atsirado greičiau nei koks nors skaitytojas įsigijo dev boardą. Tačiau softą dalinai galima pasibandyti.

Paleidus Quartus programą spaudžiam naujo projekto darymo “wizardą”. Spaudžiam NEXT ir pasirenkame direktorija kurioje kursime savo pirmą projektą. Darbo metu ten susikurs melionas ir dar biški failiukų, todėl reikia susikurti naują direktoriją. Pasirenkam projekto pavadinimą, kad ir “FPGA001”. NEXT.

Čia galima pridėti esamus failus prie projekto. Nieko dar neturim, tai spaudžiam NEXT.

Dabar pasirenkam kokią mikroschemą naudosim. Čia jau kokią prisilitavot, nusipirkot, tą ir pasirinkit. Aš renkuosi Cyclone II šeimą, 144 kojos, EP2C8T144C8. Čia pamatom, kad šitas čipas turi 1.2V core maitinimą, 8256 loginius elementus, 85 vartotojui panaudojamas kojas, 165888 atminties bitus, 36 loginio dauginimo elementus, 2 PLLus ir 8 globalius CLK sujungimus. NEXT

EDA tool settings nesvarbu kol kas. NEXT. FINISH.

Dabar dešinėje, ant “medžio” pasirenkam tą ką tik pasirinktą čipą ir spaudžiam du kartus pele. Iššoka jau matytas mikroschemos pasirinkimo langas, tačiau papildomai yra mygtukas “Device and Pin Options…”.

Čia galima pasirinkti kaip bus konfiguruojamas čipas, kokią konfiguracinę mikroschemą naudosim.

Čia gal svarbiausia mums dalis yra “Unused Pins”. Čia galima pasirinkti, kas bus su tom mikroschemos kojom, kurios nepanaudotos projekte. Naujausiam softe nusistato “As output driving ground”. T.y. sujungtos išėjimui ir nulinio potencialo. Kiti variantai irgi galimi, priklausomai nuo vartotojo norų ar PCB subtilybių. Tačiau ispėju- jei bus parinktas “output driving unspecified signal”, tai tos nepajungtos kojos turės visokius keistus tarpinius signalus iš jūsų projekto vidurių ir stipriai triukšmaus. Jei šalia stovės blogai “užterminuoti” įėjimai, tai jie gali pasigauti tuos parazitinius signalus.

papildymas. Kam reikia čia ką nors keisti. Jei naudojam kokius nors devboardus ar savas schemas, kartais projektas nesutampa su esama schema. Ir tada galima tikimybė, kad į kokias nors kojas bus paduodamas signalas. Tuo tarpu ta koja bus įžeminta per FPGA. Tai bus biški trumpas…

Dabar pasirenkam savo projektą “FPGA001” ir spaudžiam “New”. Čia renkames “Design Files” ir “Block Diagram/Schematic File”.

Kodėl grafinė aplinka “top” projekto failui? Todėl kad taip lengviau suprasti pradedančiajam ir vaizdingiau sujungti projekto signalus su realiom mikroschemos kojom.

Spaudžiam virš tuščio lauko į PIN įkoną ir pasirenkam INPUT.

Bakstelim bet kur lauke ir gautą naują piną pervadinam į ką nors žmoniškai suprantamą:

Pavadinau CLK_50MHz nes naudoju 50MHz osciliatorių ir jis bus pagrindinis projektų clock signalas.

Taip pat padedam išėjimo PINą ir jį pavadinam kad ir LAUK01. Šiuos du pinus sujungiam “laideliu”.

Spaudžiam, kad softas sukompiliuotu mūsų “schemą”.

Galima spausti arba grynai “PLAY” mygtuką arba “PLAY su varnele”. Skiriasi tik tuo, kad grynas play daro pilną kompiliacija, tuo tarpu su mygtuku kompiliuoja kiek mažiau, greičiau- nedaro galutinio bitstreemo.

Sukompiliavus, teoriškai turime patikrintą schemą- pasitikrina sintaksė ir dar galybė visokių dalykėliu. Tačiau ši schema dar “kabo ore”. Dabar reikia pririšti projektą prie hardwarės pinų. Čia profesionalai pradeda rašyti visokias komandas, o megėjai spaudžia “Pin planner” mygtuką:

Ir iššoka naujas langas su mikroschemos vaizdu ir naudojamu signalų sąrašu. Mūsų plokštėje 50MHz (ar kiek ten pas kinus) signalas paduodamas į dedikuotą mikroschemos koją “clock in” numeris 17. Tai ir įrašom apačioje (kur raudona rodyklė) 17 numerį arba pasirenkam iš sąrašo. Mikroschemos vaizde kita raudona rodyklė rodo kaip pasimato kur tas signalas eis.

“LAUK01” signalą galime paduoti į bet kurią kitą laisvą koją. Aišku signalo nelabai galima perduoti per maitinimo, žemės ar dedikuotas kojas. Jei koja dedikuota kokiam nors clock priėmimui, tai ten signalo negalima paduoti. Taip pat negalima kai kada perduoti signalus į kokias nors kojas, jei šalia esančios kojos kam nors specifiškai naudojamos. Pvz. jei kojų pora pumpuoja diferencialinį LVDS signalą, tai net per kelias artimai stovinčias kojas teoriškai negalima pumpuoti paprastų signalų- softas pyksta. Aišku galima ignoruoti tai, bet realiam pasaulyje per tas kojas kartais “girdisi” tie LVDS signalai. Tos kojos kristale ir pačiam mikroschemos korpuse stovi taip arti viena kitos, kad per parazitines talpoas signalas prasimuša. Todėl galimas neteisingas veikimas.

Aš pasirinkau 100 koją. Reikia atkreipti dėmesį, kad mikroschema turi tokias spalvotas zonas- jos vadinasi I/O bank. Čia toks navarotas, kad skirtingi I/O bankai gali turėti skirtingas maitinimo įtampas. Viena pusė 3.3V LVTTL logika, kitoje pusėje 1.5, 1.8 ar 2.5V logika ir panašiai. Mūsų plokštė visa sujungta prie 3.3V maitinimo.

Dabar, kai kojos priskirtos (matosi schemoje numeriai), užsaugojam projektą ir spaudžiam pilną kompiliaciją.

Prisigeneruoja visas kalnas ispėjimų (šis softas labai mėgsta wariningus). Tačiau visur užsidega žalios varnelės. Dabar galima softwariškai emuliuoti projektą (apie tai kitą kartą) ir dar galima supumpuoti bitstreemą per JTAG jungtį į mikroschemą ir ji persikonfiguruos pagal jūsų norus. Paspaudžiam programavimo mygtuką, jei reikią pasirenkam programatorių. Apačioje matome bitstreemo pavadinimą, koks čipas programuojamas ir netgi nedidelė schema kur matosi kaip ten sujungta. Ji aktualesnė, jei plokštėje yra kelios mikroschemos ir jos gi programuojasi per tą patį kištuką.

Kelios sekundės ir “oh my god” turime naują schemą įkūnyta hardwarėje:

Oscilografas tikrai parodys, kad 100-joje kojoje tikrai yra 50MHz (ar kiek ten pas jus) signalas.

ŠIOJE PAMOKOJE męs išmokom pradėti naują projektą, pasirinkti mikroschemą, pajungti signalus prie realių mikroschemos kojų, sukompiliuoti softą, suprogramuoti mikroschemą. Aišku, mūsų schema nieko nedaro. Bet čia tik pirma pamoka. Laukiam komentarų ir klausimų.

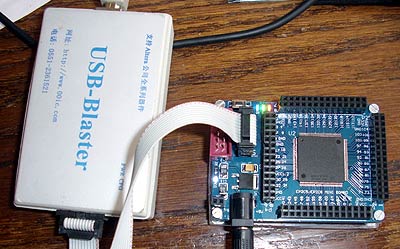

Sveiki Levai. Sudominot savo straipsniais apie FPGA. Gavau šiandien savo USB Blaster. Kol kas dar neturiu su kuo eksperimentuoti. Klausymukas – kas viduje jūsu blasterio? mano trigubai mažesnis. Viduje Silabs C8051F321 ir 74LV125.

Mano blasteris labai senas. Viduje:

FTDI FT245BL+93C46

Alteros EPM7064+24.00MHz osciliatorius. Stabilizatorius, apsaugos.

Netgi tantalinis kondikas yra. PCB irgi be taupymo.

Skirtumas akivaizdus 🙂

http://img189.imageshack.us/img189/3193/20130402190230.jpg

Pajungus nenaudojamas kojas į GND, srovės ima 230mA, vietoje 50mA padarius tri state. Kažkas trumpina? Plokštė kinų surinkta.

Tikrai trumpina kažkur. Gal padaryti Z ir su voltmetru prasisukti. Ypac prie Vio ir Vcore kojyčių. Kažkur tikrai stovi solder bridge.

Pasirodo ne solder bridge, o toks fyčiursas buvo. Kažkodėl VCC1.2 su nuliniais rezistoriais buvo pajungta prie 26 ir 81 kojų, taip pat ir GND su tokiais pat nuliniais prie 86 ir 27. Gal buvo palikta dėl suderinamumo su kitokiom mikroschemom? Nuėmus tuos rezistorius, pradėjo veikt normaliai.

Labai naudingi ižanginiai straipsniai apie FPGA! Užprogramavus panašų modulį viskas veikia, tačiau po power down-up ciklo mirgsi gimtasis kodas. Gal galėtum papasakoti kaip įrašyti kodą į eeprom’a?

FPGA tai RAM tipo įrenginys, todėl po power down, jos turinys išsitrina. Todėl reikia, kiekvieną kartą įjungus, užkrauti konfiguracinį failą (bitstream) iš konfiguracinės mikroschemos tiesiogiai, ar su mikrokontroleriu.

Konfiguracinė mikroschema (čia ji vadinasi ESPn, nors įtariu kad tai paprasčiausias 25Lxnn tipo flašas) turi savo jungtį (tokią pat, 10 pin) arba pajungta per JTAG. Su tuom pačiu programatorium ir ji užsiprogramuoja.

Tik programatoriui reikia nurodyti, kad būtent nori programuoti config čipą, ne FPGA.