Programuojama logika arba mano kančios…

Užėjo noras kiek pasimokinti apie porgramuojamą logiką. Pradinių žinių- nulis. Tik žinau, kad tokia yra.

Pati paprasčiausia ir seniausia programuojama logika tai PAL (PALCE) ir GAL mikroschemos. Deja joms reikia specialaus programatoriaus. O jo schemos internete aš neradau. Tiesa, yra GAL programatoriaus schema, bet aš jos nebandžiau. O beto softas senoviškas…

Teko pasižiūrėti į sekančios kartos mikroschemas. Jos programuojamos per JTAG (serial) kabelį ir nereikalauja specialių sudėtingų programatorių. Bėda, kad tos mikroschemos brangios ir retos. Ypač bananų respublikoje Lietuvoje, kur “support’o” megėjams visiškai nėra. O atsisiusti iš užsienio labai brangu. Teko grybauti per visokius šiukšlynus, senas plokštes. Gerai, kad tos mikroschemos perprogramuojamos (PAL – ne. Jos OTP).

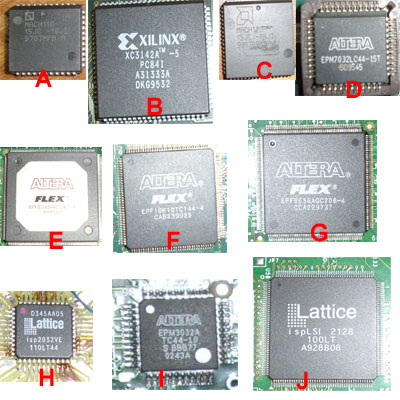

Štai mano grybukai:

(Tiesa dar turiu keleta Alteros flexu su BGA korpusais… tokie korpusai man neįkandami.)

A ir C tai AMD Mach 110 ir 120 serijos mikroschemos- neturiu softo.

B- Xilinx FPGA XC3142A, turimas softas nepalaiko jos.

D- Altera EPM7032LC44-15T – lygtai turimas softas jos nepalaiko.

E, F, G – Alteros FPGA Flex serijos (EPF10K10TC144, EPF81188ARC240, EPF8636AQC208) – tik vieną palaiko turimas softas.

H- Lattice isp2032VE110LT44 – softas palaiko.

I- EPM3032ATC44 – softas palaiko, tik schemutė veikiančiam aparate.

J- Lattice ispLSI2128 100LT- softas palaiko su “A” raide. Datasheetas sako, kad be ar su A raide tai tas pats. Bet mano readeris šios mikroschemos neatpažysta- arba mikroschema bloga, arba softas nepalaiko. Gaila. Ji man tiktu.

Kad užprogramuoti mikroschemas reikia joms sukurti jedec failus su specialiu softu. Softas brangus. O demo versijos “kramto” tik kai kurias mikroschemas. Taip susiaurino mano galimybes dar labiau.

Didelės mikroschemos turi labai daug kojų. Ir visas kojas prilituoti megėjiškom sąlygom sunku. Tai dar pamažino mano pasirinkimą.

FPGA mikroschemos labai geros, daug logikos elementų, bet jos konfiguracija saugoma SRAM atmintyje- išjungus maitinimą, konfiguracija dingsta. Konfiguraciją galima įrašyti į mažą serial ROM mikroschemą, užkrauti iš kompo per laidą ar su kokiu nors mikroprocesorium sukišti kodą ir kokio ROMo. Mano eksperimentams tai buvo kiek sudėtinga. Todėl teko pasirinkti CPLD- logika kur konfiguracija įrašoma į flash atmintį ir išsilaiko atjungus įtampą.

Deja mano eksperimentams liko tik Lattice isp2032VE110LT44.

• SuperFAST HIGH DENSITY IN-SYSTEM

PROGRAMMABLE LOGIC

— 1000 PLD Gates

— 32 I/O Pins, Two Dedicated Inputs

— 32 Registers

— High Speed Global Interconnect

— Wide Input Gating for Fast Counters, State

Machines, Address Decoders, etc.

— Small Logic Block Size for Random Logic

— 100% Functional, JEDEC and Pinout Compatible

with ispLSI 2032V Devices

• 3.3V LOW VOLTAGE 2032 ARCHITECTURE

— Interfaces With Standard 5V TTL Devices

• HIGH PERFORMANCE E2CMOS® TECHNOLOGY

— fmax = 300 MHz Maximum Operating Frequency

— tpd = 3.0 ns Propagation Delay

— Electrically Erasable and Reprogrammable

Idomu kokius FLEX’us turi BGA korpusuose? Jie atskirti nuo plokstes?

EPF10K30ABC356-2

Tupi ant plokštės. Plokštė buvo veikianti.

Kas dar tupi ant plokstes? JTAG atvirai isvestas? Jei ne, gal galima pabrobint? Siaip mane domina.

Visko ten privesta. Tai 19″ plokštė nuo 20 portų switch sekcijos.

Reikia man Xilinx FPGA XC3142A, būčiau dėkingas, jei parduotum ar patartum iš kokios technikos ją iš lupti.