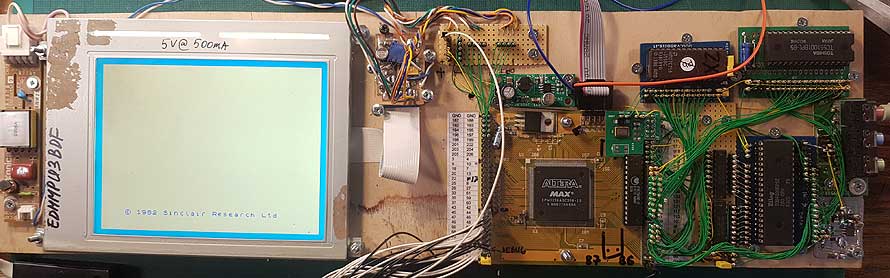

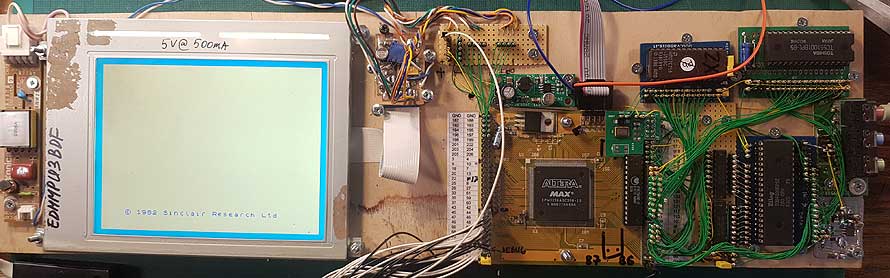

Besitvarkant daiktus (čia retas reiškinys), radau savo seną eksperimentą su FPGA/CPLD ir LCD (tik ekranas jau buvo kitas). Tas eksperimentas buvo nedabaigtas dėl žinių, noro ir kantrybės stokos. Dabar visko kiek daugiau, tai nudraskiau nereikalingas detales ir pridėjau naujų:

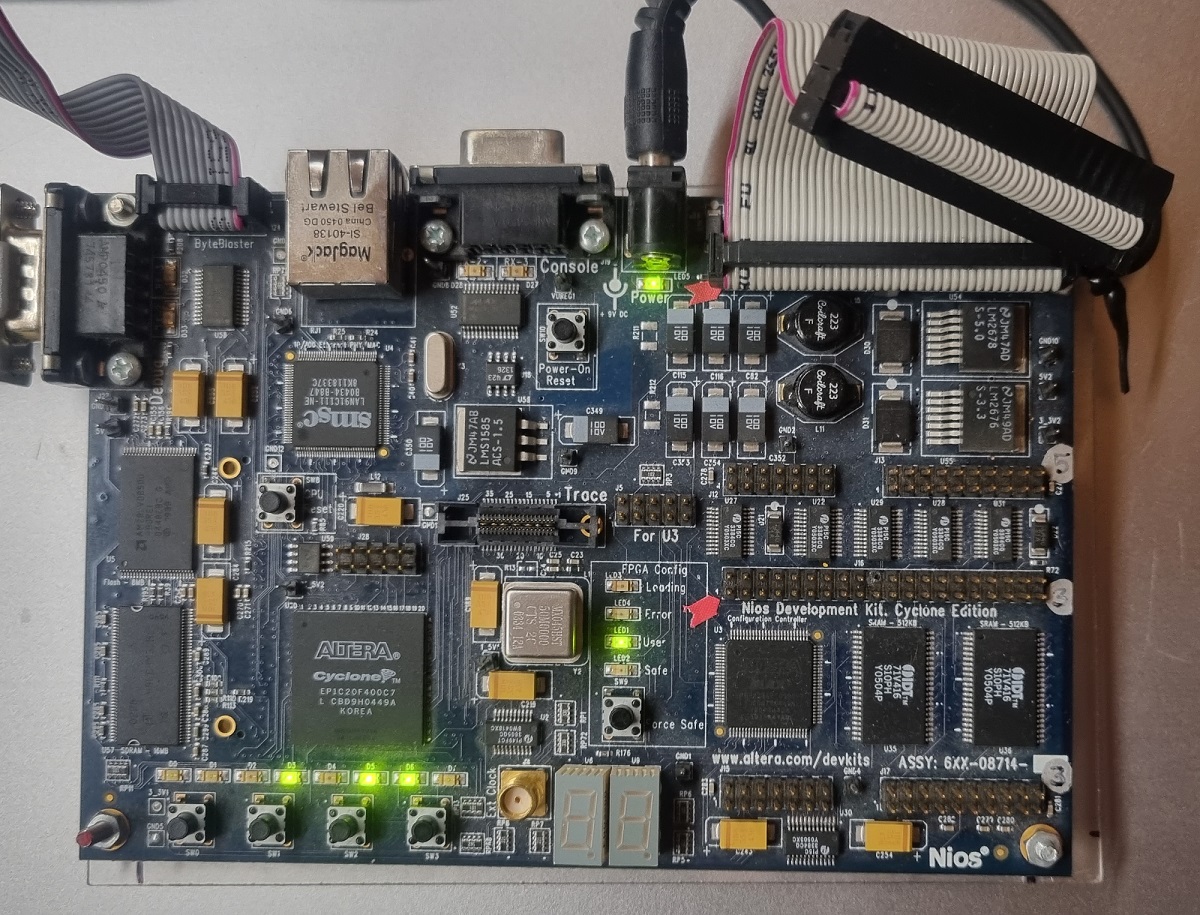

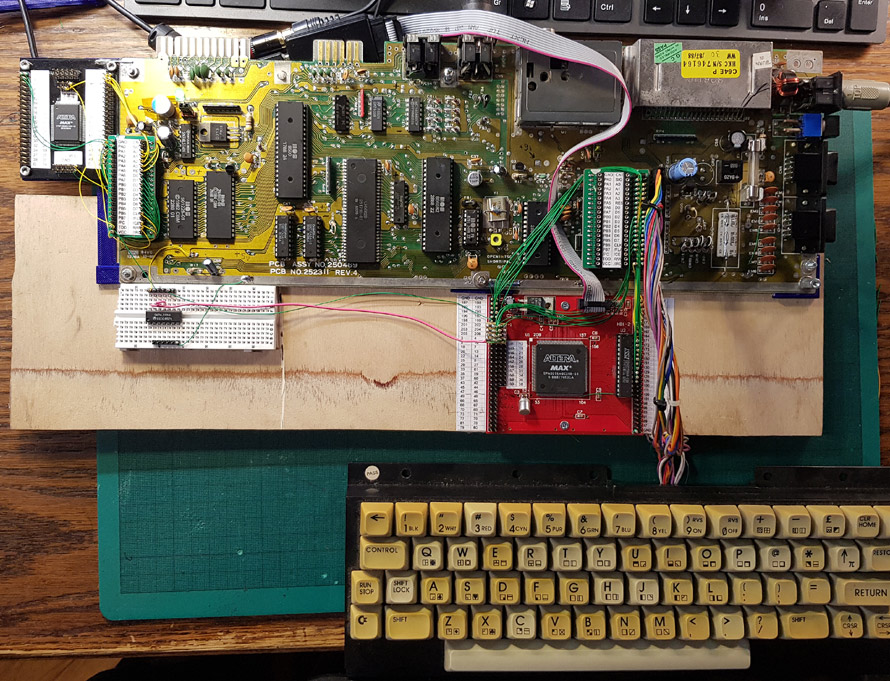

Tai labai panaši sistema kaip ir paprastam ZX Spectrum CPLD/VGA. Tik pasikeitė keletas esminių koncepcijų:

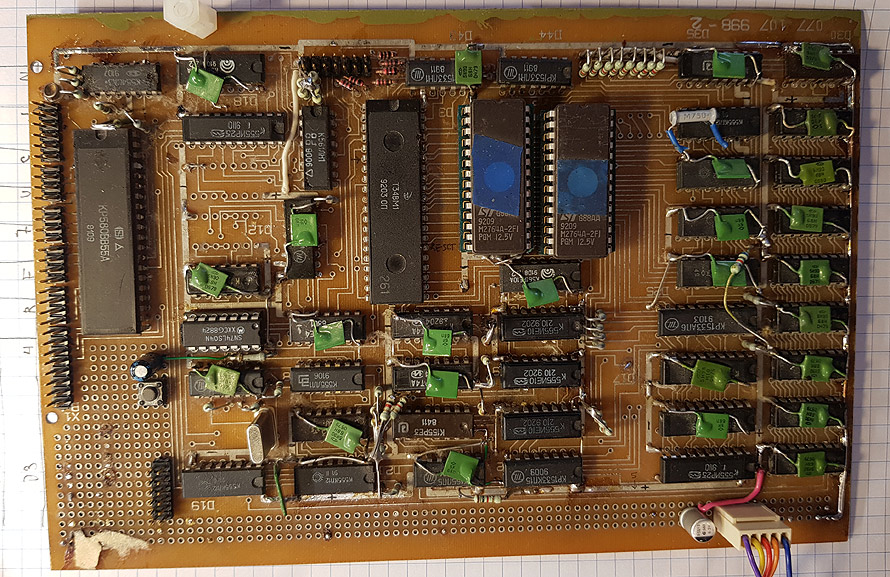

Senesnėje versijoje atmintis buvo bendra- procesorius ir VGA buferis naudojosi ta pačia atminties mikroschemą, todėl CPLD stengėsi atlikti atminties arbitro (MMU) darbą ir laiko rėžiais (time slot) prileisdavo tai CPU tai VGA prie tos pačios atminties. Ši schema kiek kitokia- pirmiausia, naudojama atskira atmintis procesoriui- Toshiba TC551001BPL-85. Tai žymiai lėtesnė atmintis, tačiau ji skirta tik procesoriui. VGA ar LCD kontroleris visiškai nesikreipia į ją. LCD/VGA kontroleris tik sėdi ant duomenų ir adreso linijų ir stebi jam reikiamas kombinacijas- jei pastebimas rašymas į video atminties plotą, duomenys dubliuojami ir LCD/VGA atmintyje. Taip pat stebim Z80 IN/OUT veiksmus, nes mums reikia vaizduoti pajungta klavietūrą, magnetofoną ir garsiakalbį.

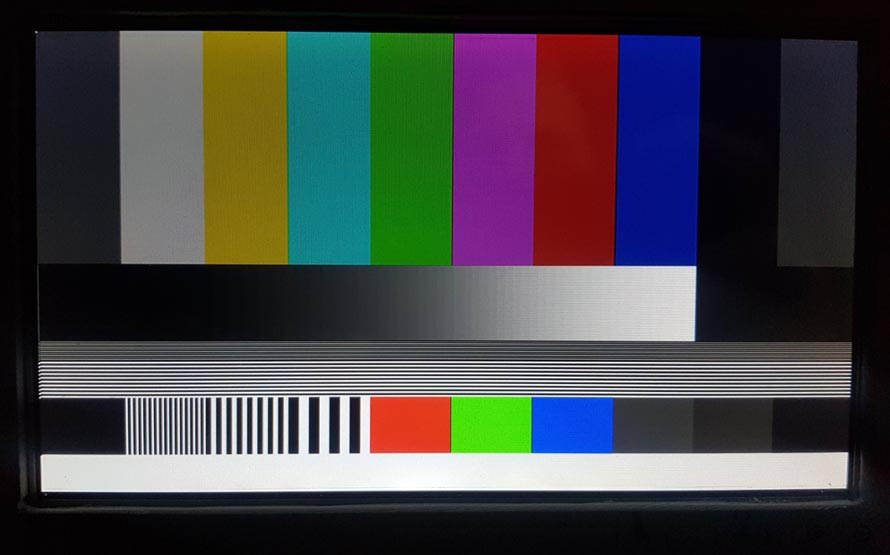

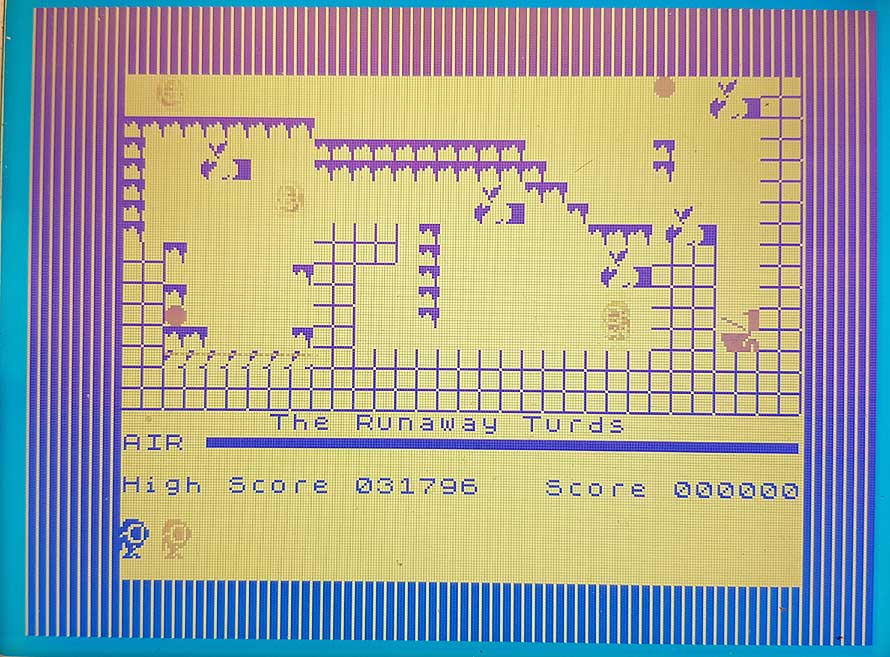

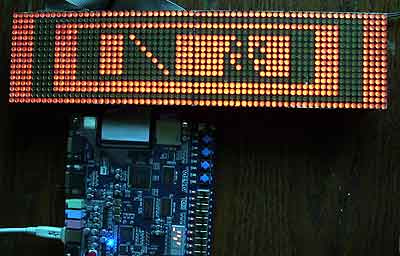

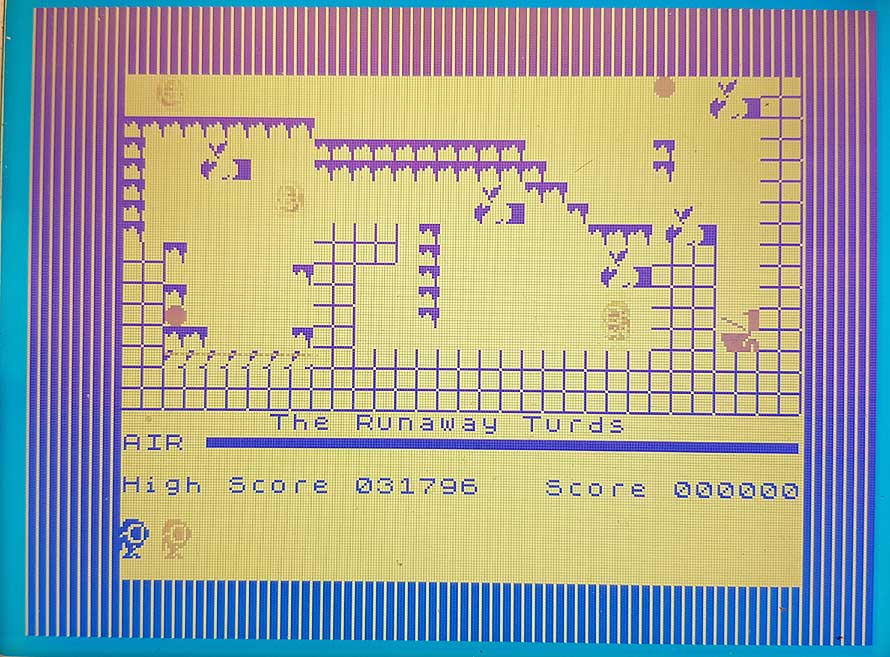

Tačiau tai vienspalvis LCD monitorius, 320 x 240 taškelių. Duomenys pumpuojami po 4 bitus iš karto, todėl sistemos dažnis netgi kiek lėtesnis. Tačiau labai lėtinti negalima, nes kažkur prie 40Hz kadrų dažnio labai matosi vaizdo mirgėjimas. Dabar LCD veikia virš 60Hz dažniu. Deja, jis labai inertiškas- “border” efektai susilieja…

O judantys objektai beveik nesimato.

Aišku šiame variante visiškai ignoruojami spalvų atributai (“flash” veikia), todėl žaidimų vaizdeliai keistoki. O borderį padariau dryžuota, kad kiek nors skirtusi “spalvos”.

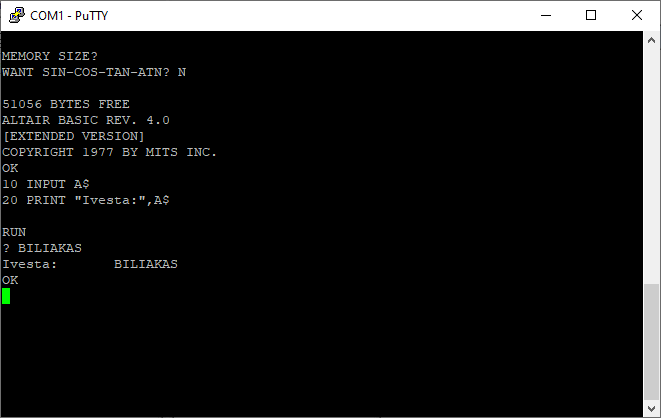

Šis antras maketas buvo surinktas ne dėl ZX spectrum. Aš galvoju čia sudėti kokį nors kitą retro kompiuterį, bet ZX yra vienas iš paprasčiausių, tai testavimui suėjo.

Schemotechnika visiškai paprasta- adresų šyna po stiprintuvo 2x SN74HCT541N (nelabai jis reikalingas) eina į CPLD, ROM, RAM. Tas pats, tik be buferio, padaryta su duomenų šyna. Viskas “sumontuota” CPLD mikroschemoje. Ten aišku tebeliko keletas klaidų, tačiau sistema veikia.

Ir aišku visi failai:

Intel-Altera Quartus CPLD source code for ZX Spectrum LCD version.

Jei jums nepasileido, tai atminkite, kad kai kurie Z80 CPU reikalauja, kad jų clock būtų 5Vpp, o ne TTL lygio.

LCD ekranas iš senoviško dauginimo aparato: EDMMPU3BDF, jo pinout:

1. ON/OFF

2. n.c.

3. VS

4. HS

5. pix CLK

6. Vcc, +5V

7. GND

8. Vee, -25V

9. D3, pixel data

10. D2

11. D1

12. D0

13. Vee, same as 8.

14. contrast.