Buvo nuo senų laikų prikaupto Cikloninio šroto. Viena bėda- BGA korpusas. Tačiau laikai keičiasi, ketursluoksnės PCB jau pigios ir iš garažo buvo ištrauktos mikroshemos. Plokštė gavosi su viena rimta klaida, bet šiaip viskas veikia. Reikia pagirti Alteros mikroschemos tvirtumą. Ji buvo lituota fabrike, poto aš nulupau. Poto bandžiau reballinti, poto dar bandžiau, poto dar bandžiau. Poto prilitavau, bet ne iki galo. Poto dar kaitinau ir tapšnojau, kad rutuliukai susijungtu su PCB. Ir mikroschema išlaikė šiuos išbandymus.

Šis ciklonas turi PLL ir turi LVDS išėjimus. Kaip tik išbandyti HDMI (DVI) interfeisui:

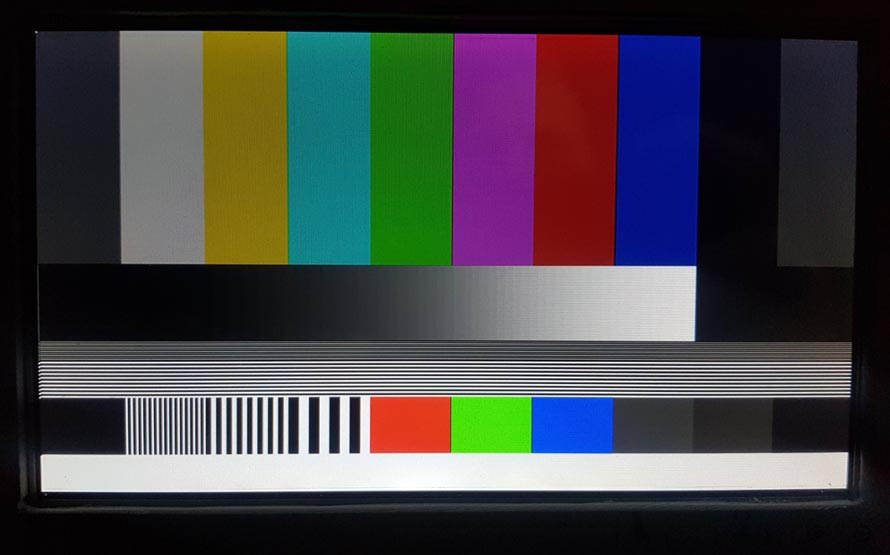

Čia mano kiniško monitoriaus ekrano nuotrauka. Signalas eina tiesiai per HDMI iš FPGA. Matosi viena problema- eilutėje su vertikaliais brūkšneliais, pats kairinis turi būti irgi dryžuotas. Dabar neaišku, ar čia kaltas mano projektas arba visdėlto kiniškas upscaller. Mano “generatorius” išduoda VGA (640×480@60Hz, 25MHz pixel clock) vaizdą, o kiniškas žaislinis monitorius lygtai FullHD.

Pačio “generatoriaus” nuotrauka:

Mano PCB su FPGA, toliau yra nematomas izoliatorius- grupė kondensatorių. Nes monitoriaus 3V labai dažnai nesutampa su FPGA 3V ir gali nunešti kojytes. Nors HDMI duomenys taktuojami 250MHz dažniu, bet dėl naudojamo “skremblerio ir DC naikintojo” (TMDS) duomenų porose dažnis kažkur apie 25…30MHz, HDMI clock- 25MHz (biški neatitinka standartui). Bet lygtai veikia. Yra bugų- rodos viršuje ekrano (koordinatė 0,0) liko vienas pixelis iš ekrano apačios ir prie grayscale biškas kažkas neteisinga. Bet jau tingiu tikrinti verilogo formules.

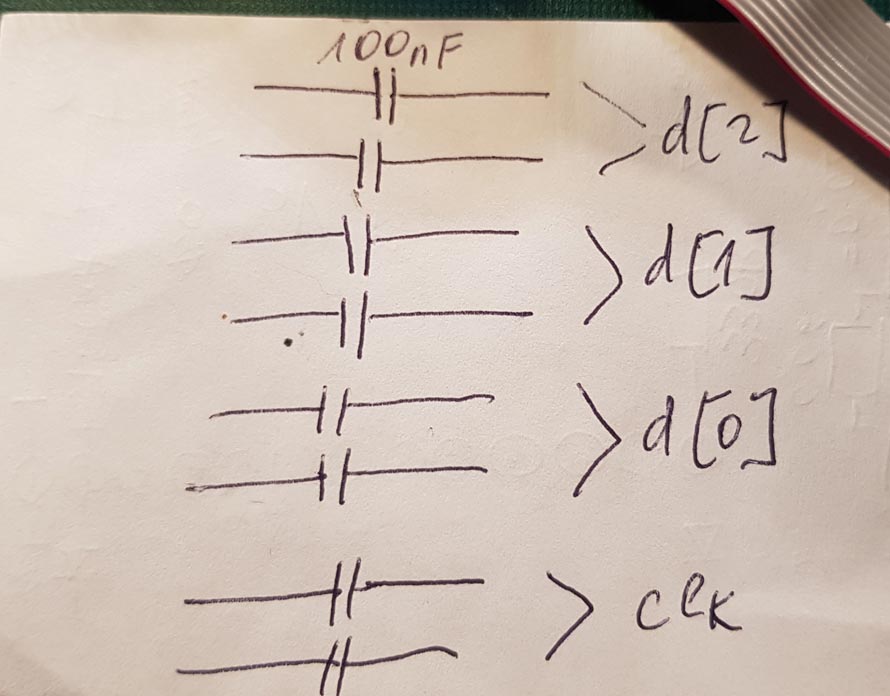

O čia tiems kurie nesuprato HDMI prijungimo schemos, beja internete irgi reikia pasiknaisioti kol surandi.

Nesu tikras, ar tikrai tokie dideli kondensatoriai reikalingi.

Pats Altera Quartus archyvas su viskuom: Quartus Archyvas, HDMI tester Cyclone II verilog.