Internete yra gana daug viskiausių VGA signalo generatorių schemų FPGA čipams. Vienos geriau, kitos mažiau suprantamos. Tačiau radau vieną aiškinimą kuris man pasirodė labiausiai suprantamas ir lengvai realizuojamas.

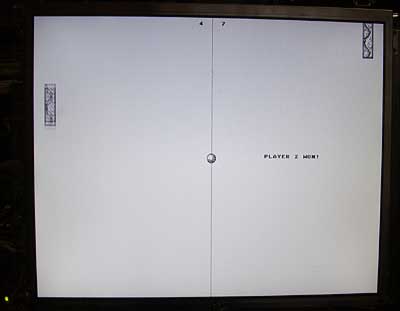

Pradžiai reikia pažiūrėti į paveikslėlį:

Tai visas video signalo vaizdas- balta zona tai tas ką męs matom ant ekrano, kitos dalys- nematomos, bet labai svarbios.

VESA numato visą eilę standartinių video siganalų ir raiškų variantų. Mane domina tik patys populiariausi- naudojami LCD ekranuose (native resolution) ir paprastieji VGA režimai kurie buvo naudojami su CRT monitoriais.

Dažnas žino ekranų raiškas (800×600, 1024×768), dar gal kadrų dažnį (60, 70, 75 … 100Hz), tačiau žymiai mažiau žinomi kiti labai svarbūs parametrai- pixel clock ir eilučių dažnis.

Yra dar sinchronizacijos signalai, jų ilgis, dažnis, vieta ir poliariškumas taip pat standartizuoti.

Darant VGA signalą geriausiai skaičiuoti x ir y koordinates ne iki standartinio ekrano dydžio, bet iki viso signalo galo. T.y. VGA režime x reikia skaičiuoti ne iki 640 taškelio, bet iki 800. Tada labai lengva realizuoti teisingus sinchro signalus- po vaizdo palaukiam 16 pixelių (A), padarom sinchro signalą ir palaikom 96 pixelius (B), pašalinam sinchrosignalą ir dar 48 pixelius laukiam iki naujos eilutės pradžios (C). Panašiai ir su y koordinate.

Dabar biški VESA standartinių duomenų:

| Mode | Pixel clock, MHz | VS, Hz | HS, kHz | Sinchro poliariškumas | x | y | A | B | C | D | E | F |

| VGA 60 | 25.17 | 60.04 | 31.46 | – – | 640 | 480 | 16 | 96 | 48 | 11 | 2 | 31 |

| VGA 75 | 31.5 | 75 | 39.38 | – – | 640 | 480 | 16 | 96 | 48 | 11 | 2 | 32 |

| VESA 1024×768 | 65 | 60 | 48.36 | – – | 1024 | 768 | 24 | 136 | 160 | 3 | 6 | 29 |

| VESA 1280×1024 | 108 | 60 | 64 | + + | 1280 | 1024 | 48 | 112 | 248 | 1 | 3 | 38 |

Jei domina kitos rezoliucijos, va online skaičiuotuvas: http://www.tkk.fi/Misc/Electronics/faq/vga2rgb/calc.html

Šiaip dažniai gali vos vos skirtis- monitorius sugeba prisiderinti prie nedidelių nukrypimų, bet geriau daryti tiksliai. Darant schemutes su FPGA ir naudojant VGA režimą, galima pernelyg nepaisyti elementų vėlinimo, tačiau darant projektą skirta normaliam LCD monitoriui taimingas labai svarbu- 100MHz pixel clock tai jau ne juokas. Čia galioja ne tik vėlinimas išorinėje atmintyje, bet ir vėlinimas pačioje FPGA mikroschemoje.

Vienas iš geriausiu prietaisų pasitikrinti vėlinimus yra LCD monitorius dirbantis “native resolution”- 17″ monitorius tai “tikslus oscilografas” su 10ns “raiška”.

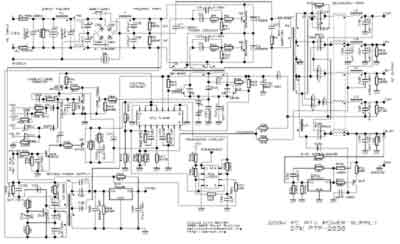

Pavyzdinis Verilog failas VESA 1027×768 vaizdelio generavimui (rodo kelius brūkšnelius):

Continue reading →