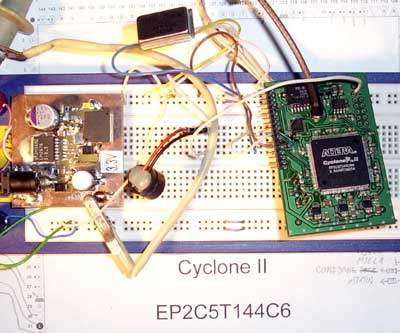

Kaip jau seniau minėjau, viena firma “davė” keletą plokštelių su ALTERA FPGA Cyclone II (EP2C5T144C6N). Jos buvo išbrokuotos dėl kažkokių tai priežasčių. Kiek apžiurėjus PCB buvo pastebėta, kad kaikurios plokštės perpiltos lydmetaliu, o kitos kiek perkaitintos ir takeliai vietomis susibanginiavo. Išsirinkau kiek mažiau pažeista plokštelę ir nutariau kiek paburti. Pirmiausia, plokštelėje nėra JTAG kištuko, bet yra skylė jam. Įlituojam jį. Ant plokštės sumontuoti core ir kiti stabilizatoriai atrodo nepažeisti. Pajungiau 3.3V maitinimą ir … plokštė atsiliepė JTAG grandinėje.

Tačiau, nors ir leidžiasi programuojama, bet nepereina į “user” režimą. Kiek panagrinėjus takelius ir prasisukus su oscilografu, pamačiau, kad mikroschema pajungta kitam programavimo režimui. Teko kelias valandas paburti ir štai rekomendacijos: reikia susirasti vieną naują mažytį SMD rezistorių apie 10K vertės ir trys mažus laidukus. Geriau naudoti taip vadinamus “Kynar wire” t.y. plonas monolitinis laidelis su izoliacija kiek plonesnis už plauką.

Nupjaunam takelį nuo 85 kojos (MSEL1) kuris einą į vieną iš stabilizatorių. Su lituokliu paimam lašiuką lydmetalio ir užtrumpinam tarpelį tarp 85 ir 84 (MSEL0) kojos. Čia turi gautis, kad abi kojos pajungtos į žemę. 10K rezistorių vienu galu lituojam prie Vcc 3.3V. Prie kito galo prilituojam laiduką apie 10mm ilgio ir jungiam jo kitą galą prie išorės kištuko adatėlės kuri eina prie 15 (DCLK) kojos. Taip padarom DCLK pull up. Kitą gal net trumpesnį laidą prilituojam prie žemės, o kitą gala prilituojam prie kištuko adatėlės kuri eina į 14 (DATA0) koją. Dabar idomioji dalis- ant plokštės stovi LCX125 (buferiukai paprasčiausi). Galima juo panaudoti, bet paprasčiau (bent jau man) tai nutraukti takelį iš LCX125 6 kojos einanti į cikloną. Tai patogu padaryti kitoje plokštės pusėje. Toliau plonu laideliu reikia nutrauktą takelį einanti į cikloną sujungti su Vcc 3.3V, juolab kad čia taip patogiai jis eina ir yra abieju signalų VIA skylės.

Žodžiu turi gautis taip: 14 (DATA0)=GND, 15 (DCLK)=PULLUP, 16 (nCE)=GND, 20 (nCONFIG)=VCC OR PULLUP, 82 (nSTATUS)=PULLUP, 83 (CONFDONE)=PULLUP, 84 (MSEL0)=GND, 85 (MSEL1)=GND.

Plokštėje yra kažkokios paslaptys susijusios su šoniniu kištuku, kažkodėl ant jo išeinantis signalai kažkaip dubliavosi, nors to neturėtų būti. Dar neišsiaiškinau- bet padavus signalą iš ciklono, ten pasidubliavo kai kurie išėjimai ir pats ciklonas kiek pradėjo šilti. Tačiau eksperimentams visai tinka ir kita skylė skirta kažkokiai jungčiai- ten yra 12 kontaktų ir kurių 11 pajungta prie “atsarginių” ciklono kojų (113, 112, 115, 114, 121, 118, 125, 122, 133, 126 ir 134). Dvylikta koja tai žemė. Taktiniam dažniui patogu naudoti šoninį kištuką, jo viena adatėlė eina per 56 omų rezistorių į 17 (CLK0) ciklono koją.

Ciklonas bent jau per šias kojas puikiausiai dirba ir programuojasi. Dėkui už mikroschemą.

Ziurint i postus matosi kaip stipriai linksminiesi 😉 Bendrai daiktas yra FPGA, tik dabar nera kada uzsiimti darbai prispaude… Man is idomesniu dalyku kuriuos galima padaryti su FPGA tai logikos analizatoriai (tarkim http://www.freepcb.com/eebit), netgi nebutina rasytis super soft’o, galima surinktus duomenis tiesiog is FPGA->MAX3232->PC-> Hyper terminal’a nusimesti i Excel’i. Paskiau su gautais 0 ir 1 darai ka nori nori verti i hex’a, nori su grafiku funkcija subraizai laiko diagramas skirtingiems kanalams. Galima “pasiklausyti” I2C, SPI, 1 Wire ir t.t. ir pan., tam turetu uztekti ir vidinio BRAM’o. Pigu ir velka iki 100 – 200 MHz jei prikabint SRAM’uka.