Supumpavau Verilog kodą iki tiek, kad pagaliau RGB matrica pradejo rodyti beveik 24 bitus informacijos. Kadangi neteisinga tiesinė LED priklausomybė, labai daug informacijos išsikraipo ir nesigauna didelis grožis. Diodų šviesumo ir žmogaus akies priklausomybė greičiausiai kokia logaritminė. Ir dar trūksta taktų (PWM moduliacija vykdoma pakadriui, nes taip sujungta schema. Todėl fps turi būti x kartų didesnė nei standartinė flicker-free), jei imti 256/4 mirgėsio nėra, o štai prie 256/2 jau jaučiasi žiaurus mirgėjimas. Taktinis dažnis ~120MHz. Nėra kur slėptis.

Keletas iliustraciju:

Kaip viskas šviesu ir negražu. Visai nėra juodos spalvos. Tuo tarpu originaliam paveikslėlyje irgi nėra juodos spalvos, bet daug “tamsiai pilkos”:

(2K kosminė odisėja ir demotivatoriai)

Labiau “hentai-manga” stiliaus paveiksliukas su popieriaus lapu:

ir visas, nufotkintas tamsoje:

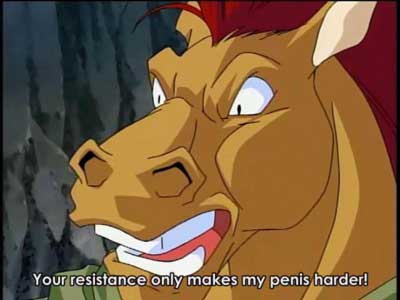

Originalus paveiksliukas:

“Your resistance only makes my penis harder!” posakis yra gana įžymus, žiūrėkit vikipedijoje apie tai. 🙂

Testinis failas (SOF/POF) įrašyti i FPGA ar konfiguracinę mikroschemą EPS4: POF/SOF.POF/SOF (fixed). New: POF/SOF. Naujos “firmware” source kodas.

Seip o jei pritaikyt kokia gamma funkcija priesh sheriant duomenis i ekrana ?

Galima ir pritaikyti, bet norėtusi pirmiausia sužinoti tuos dėsnius kuriuos reikia pritaikyti ir norėtusi viska sugrusti į pačią matricą- ten dar daug laisvos logikos liko.

Galutine mintis- prijungti SD kortele ir kad is jos nusikrovinetu paveiksliukus. Į pačią kortelę duomenis surašyti be failų sistemos.

16 diodų patamsėjimo problema:

Nežinau tiksliai kame problema, bet ji atsiranda tik tada kai uždegami visi 16 diodų ant vienos MBI mikroschemos. Tiksliau efektas yra visada- kuo daugiau diodų dega, tuo silpniau jie šviečia. Ir skirtingai ant visų spalvų. Atrodytu, kad neužtenka įtampos. Bed sėda ir mėlyni diodai, tai reiškia ir 5V grandinėjė yra tas nusėdimas. Ir dar, tas efektas pasireiškia ir toje matricos dalyje kur nėra 8 diodų- užtenka “uždegti” neegzistuojančius diodus ir bendras vaizdelis nusėda. MBI datašyte apie tai nieko neparašyta. Maitblokis irgi gana galingas- 250W ATXas, su feedback ant 3.3V grandinės.

Prigesusių diodų problema išspresta- pasirodo užlenkiau aš taip vadinamo “white balance” PWMo dažnį. Ji sumažinau ar tai 5 ar 4 kartus ir bėdos dingo. OE išėjimas matyt nesuspėdavo su mano dažniais…

Gražu 🙂

Any chance you’ll be publishing the verilog? Are you scanning each row several(256?) times? Did you end up replacing the reference current resistors on the mbi chips to achieve good white balance or accounting for it in the fpga?

Thanks as always.

-Ian

I will publish source code in near future. As soon as I’ll catch all bugs.

I use less than 256 levels, in such device there is no need for full 24 bit RGB graphics.

About white balance: the design of the board is using “selected” LEDs, so the whole board is even in all banks. All you need to set primary white balance for whole board. This is done PWM’ing OE pins of MBI drivers. In my design, there are 3 bytes of ROM to set master white balance. Next problem is the “gama”. I desinged FPGA, that there is “gama” lookup table (in current version for all colors same, but in future- each R, G and B will have its own gama table). Now I am working with gama table values- writing software in MS basic to generate data table.

How do you communicate with the FPGA? Are you using LVDS interface?

I also have one of this board and I begin to design the FPGA ‘code’.

Thanks for your nice work!

Mathieu.

I am stuck in LVDS stage. Can’t synchronize data bits using UTP LAN cable connection…

[…] nepasimestu kietam diske. Čia mano turimos RGB matricos FPGA programulka. Rezervinė […]