Mintis paprasta- reikėjo padaryti LVDS siuntiką mano RGB matricai. Nei viena turima testinė FPGA plokštė netiko. Vienintelė išeitis- darytis plokštę. Viena problėmėlė- CycloneII mikroschema turi 144 kojas ir 0.5 mm kojelių žingsnį. Buitinėm sąlygom kiek sunkokas variantas- reikia užsisakyti kokiam nors fabrikėlyje Kinijoje ar Bulgarijoje. Tačiau tokia PCB gana brangiai kainuoja. Ypač žinant tai, kad aš dar nežinau kaip kas turi būti padaryta. Todėl išmasčiau, kad “beta” versija reikia pabandyti pasidaryti namie. Tokiom mikroschemoms reikia daugiasluoksnės plokštės, tačiau namų sąlygom metalizuotos skylutės nesigauna ir šiaip problemos su sluoksnių sutapatinimu. Todėl plokštę pasidariau viensluoksnę.

Va paveiksliukas kaip turi atrodyti plokštė:

Rausvais kvadratais pažymėtos vietos, kur padariau klaidas. Klaidos tokios:

- FPGA I/O 2.5V, ATMEGA16 3V tačiau aš neturėjau L versijos. Todėl mega važiuoja ant maždaug 5V.

- Megos I/O ir Ciklono I/O lygiu suderinimas. Bandom su rezistoriais.

- Rezonatorius ??MHz buvau sugalvojęs viena, teko dėti 50MHz kuris irgi važiuoja ant 5V. Iš čia CLK lygiu suderinimas su rezistoriu ir diodu. Kiek jis duoda problemų dar nežinau.

- FPGA PLL maitinimas. Čia jau aš kaltas, kad iki galo neįsiskaičiau į instrukcijas. Aš sujungiau PLLA ir PLLD laidelius į vieną laidą ir per ferituko ir kondiko filtrą pajungiau prie VCCINT… Galbūt dėl šito negaunu PLL LOCKED patvirtinimo LVDS išėjimo megafunkcijoje.

- Dar nepatvirtinta, bet rodos supainiojau “p” ir “n” poras ant kištukų… nes duomenys kitame kabelio gale gavosi invertuoti :).

- Užmiršau “apsauginius” 3.6V zenerius ant USB duomenų šynos. Ir vieną rezistorių ten pajungiau prie GND vietoje VCC5.

Viena LVDS pora neveikia. Nežinau kodėl. Pasirinkau vieną kojelę su “dual purpose pin” ir kažkas man ten gliučina.– radau mažyti “solder bridge”- Nenumačiau keletos vietų “demferiniams” kondikams, nors ant PCB ten vietos pilna.

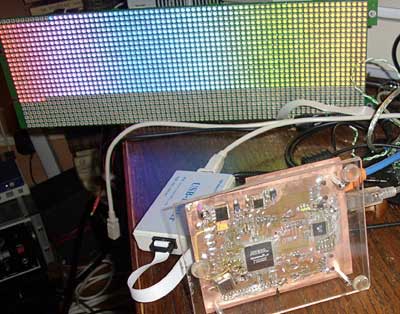

Pagaminta plokštė, kad negalvotumėte, kad svaigstu. Tas organinis stiklas tikrai padeda, nes ne vieną prietaisiuką esu pagadinęs kai nusprūsta koks oscilografo žemės laidas ir prisiliečia prie ten kur nereikia.

(Plokštė pagaminta su fotorezistu ir lazeriniu printeriu. Takeliai išvedžioti Eagle programa)

Kol kas viskas veikia blogai. RGB LED plokštė pagauna LVDS sinchronizacija, bet vistiek bando rodyti visokius briedus. Pagyvensim pamatysim, kol kas gi mokomės. Dar nei vieno LVDS projekto nedariau.

O projekto fantazija buvo tokia, kad iš kompo informacija per USB paduodama į šią plokštę, o ji, savo ruožtu, valdo vieną arba dvi RGB matricas.

Šiuo metu, matrica prijngta 100Mbit greičiu prie “valdymo” plokštės. Jei pavyksta sekmingai sinchronizuotis, duomenys teisingai vaikšto ir matrica valdosi (per JTAG). Tačiau siuntėjo LVDS modulis “PLL LOCKED” nepakelia.

Tikrai įdomu skaityt, nors ir nieko nesuprantu;D

Tikslas toks paprastas, o trasa vingiuota, bet ko gi nepadarysi dėl sporto

Laukiam finišo, kuris bus nepastebimas, bo už jo dar ilgesnė trasa

O kodel nepabandzius P-CAD ploksciu daryti ?

O koks skirtumas koks softas? Sunkiausia ne nusipaišyti, bet padaryti plokštę “iš metalo”.

[…] Mažoji (master) plokštelė tai antras Alteros ciklonas (kurį man antrinių žaliavų pavidalu padovanojo Lietuviška elektronikos firma su trumpu pavadinimu iš T raidės). RGB matrica– tai jau seniai iš eBay nupirkta pramoninė matrica su pirmos eilės ciklonu. Plokštės sujungtos mėlynu lanksčiu UTP LAN kabeliu nuo telekomo DSL modemų. Duomenų perdavimo greitis 2*100Mbit. Manau galimas ir didesnis, tik neaišku ar man didesnio reikia. […]