Pradėjau paišyti PCB skirta pajungti mano RGB matrica(s) prie kitų įrenginių ir nusprendžiau, prieš darant eksperimentus kiek paeksperimentuoti. Tada pačiupau senesnę savadarbę plokštę su Altera Cyclone 1 minimaliu čipuku su 100 kojų. Gerai, kad neskaičiau datasheeto, nes vėliau išskaičiau, kad 100 kojų pirmasis ciklonas nepalaiko pilnaverčio LVDS… Bet kažkas gavosi. Apie LVDS subtilybes nieko nežinojau, todėl teko pradėti nuo nulio. Ir dar viena bėda, kad reikia konstruoti du prietaisus- siustuvą ir imtuvą. Ir neaišku kurioje vietoje yra klaidos 🙂

Iš pradžių bandžiau daryti be PLL, nes jų trūkumas šioks toks… O štai vizardai kai užsispyre neleidžia naudoti mažų greičių. Iš pradžių bandžiau 100 megabitų greitį, bet gavosi tik su 200 megabitų.

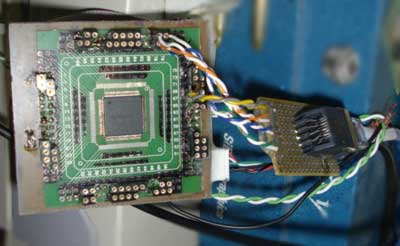

Pats primityviausias siustuvas. Tikrai jo PCB nepritaikyta LVDS signalų siuntinėjimui. Toliau eina apie 2 metrai mėlyno, lanksčio UTP lan kabelio…

O čia paprasta iliustracija. Paleidžiam abu “aparatus” ir ištraukiu ir vėl ikišu LAN kištuką:

… ir kai atsigauna vaizdas, tada galiu ramiai per JTAG keisti “siuntėjo” RAM turinį ir duomenys puikiausiai persiduoda per tą kabelį.

(apačioje vaizdas iškraipytas todėl, kad pas siuntėją mažai atminties)

O šita sinchronizacijos bėda kol kas man nesuprantama.

Truputi techninės informacijos: Siuntėjas Cyclone EP1C3, taktinis dažnis 25MHz, toks pats dažnis ir persiunčiamas per vieną LVDS porą (3V). Siuntėjo viduje stovi dviejų kanalų x8 serializeris. Gautusi kaip ir 16 duomenų bitų. Tačiau aš duomenim naudoju tik 8 bitus, o likusius aštuonis naudoju tik adreso sinchronizacijai- paprasčiausiai siunčiu RESET signalą.

Imtuvas pasiima 25MHz taktinį signalą, susimaitina į savo PLL ir priima duomenis.

Ir šiaip šitas “negeras” rodymas kažkaip susijes su bitų seka. Nes transliuojant B/W ($00 ir $FF) vaizdą “kokybė” žymiai dažniau būna gera ir taškeliai visada užsidega savo vietoje.

Video kai kaišiojamas UTP kištukas:

Jau radau vieną klaidą mano naujojoje PCB. Tiesa, ji nėra esminė.

puikus eksperimentai prieš ekperimentuojant 🙂

Su naujais!

One thing to be aware of according to Kevtris is that the twisted pairs for the LVDS are not the same pairings as in a straight-through ethernet cable. He made his own cables.

I suspect this is more a clock domain/data issue than a hardware issue though.

I also have not yet finished with LVDS on my 24×32 panels (I am still writing introductory code) so I am talking out my butt, but I figured this might help.

My cable is good. I made connections according LED board. When I received bad results, I tested it with LAN cable too… same results. I even tested it with 10cm cable… same shit. I think there is some error in my design. I reduced data rate to ~6Mbits and at least I have very stable data. I only need to create some module to resync system.

Lastest “firmware” source code: Quartus Archive for RBG LED matrix full color.