Nupirko šrotines ADSL bazines stotis, pačios pirmosios kartos Nokijas ir Siemensus. Šiaip visokių 19″ racku pilnų elektronikos, kažkiek Cisco tinklinės įrangos. Elektronika specifinė, plačiai vartojamu detalių nėra. Užtat yra daug FPGA ir CPLD čipukų.

Čia idomesnė elektronika kurią atsinešiau namo nusikrapštyti idomesnes mikroschemas. Pagrinde domina FPGA, tačiau man tinka tik nedidelės (fiziškai) mikroschemos ir nelabai naujos. Naujosios jau BGA korpuse, o tokį namų sąlygom nepanaudosi. Tas pats ir su senom, bet labai dideliom mikroschemom- 240 plonų kojyčių tai jau labai daug.

Pagrinde tokios mikroschemos- Altera Flex’ai ir Max’ai pas optinius imtuvus, o štai ADSL skirstytuvai turi Arijas. Yra ir konfiguracinių čipų. Seni flexai geri dar tuo, kad jom užtenka vieno maitinimo šaltinio, tačiau neturi navarotnų PLLų. Dar yra visokių egzotinių atminčių- nuo IDT ar Cypress dviporčių statinių ramų iki Samsung ar Mitron SDRAMų.

Biški fotkių toliau:

Eilutė BGA Flexų, nelabai ir panaudosi. (EPF10K50EFI256)

Flexus kairėje (kur 4 vienodi) jau sėkmingai litavau. 5V maitinimas ir viskas. (EPF10K20TC144 ir EPF10K10QC208). Dar su lipdukais EPM7064TC44 (kai kada su S raide, kai kada be).

Dideli FLEXai ant daughter boardų. Nzn. kojų per daug. (EPF10K40RC240, EPF10K30RC208)

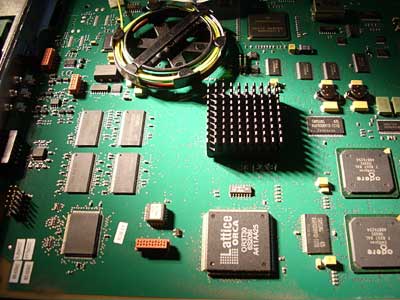

Lattice ORCA irgi rimtas čipas. Šalia jos yra konfiguracinis čipas. Po optinio kabelio “katuška” pasislėpęs Alteros čipas. Bet BGA korpuse.

ORCA- OR3T30 (48K system gates, 1568 LUTS, 2463 registers, 25K RAM, 224 I/O…)

Dar geras dalykėlis- DC/DC keitikliai. Iš ryšininkų 48…60V į populiarias įtampas- 12, 15, 5 ar 3V. Tokios gražios kaladėlės įvairaus galingumo.

kur tu panaudosi tus cipus?

Kur panaudosiu? Bet kam, yra pilna internete projektėlių. O ir jais naudotis paprasta- softas programavimo nemokamas ir palaiko visus senus čipus (čia apie Altera). Į didelius čipus galima ikišti ir procesorių. O labiausiai patinka, kad didelis greitis, paralelinis veikimas ir galima n-kartų pertaisyti schemas.

Gaila, kad nėra ciklonų- ten daugia navarotų viduje.

tipo irasius i cipa programa galima istrinti ir vel irasyti?

o i atmega mikruskes negalima ane? irasei karta ir fsio

Tu matyt nežinai kas yra FPGA? Jei lyginsime ATMEGA ir FPGA, tai į atmega gali įrašyti softą ir perrašyti. Jei reikės kokio nors hardwarinio dalykėlio reikės keisti mikruškę. Į FPGA galiu įrašyti ATMEGA ir vėliau įrašyti softą. Arba galiu įrašyti PICą ar MC68K procesorių. Arba pasidaryti savo ATMEGOS variantu su naujom komandom ar papildomais pinais.

Tačiau pagrindinis navarotas- lygiagretus skaičiavimas ir greitis. Jei algoritmas leidžia apdoroti signalą lygiagrečiai, tai ir apdorojam jį lygiagrečiai ant max greičio. Pvz. RGB matricos projekte duomenys iš LVDS (Per LAN kabelį, 100 ar 200mbitų) padedami į vidinę atmintį, tuo pat metu duomenys iš tos atminties skaidomi pagal kadro numerį (daroma PWM moduliacija keliems tūkstančiams RGB LEDų) padedama į buferinę atmintį, ir tuo pat metu skaidoma į 30 kanalų ir per serial shift buferius pumpuojama į periferijos mikroschemas. Kai kuriose schemos vietose greičiai virš 200MHz- RAMas net nespėja veikti ir aš tuo pasinaudojau- įrašau duomenys į atmintį ir tuo pat metu nuskaitau SENUS duomenus iš atminties, nes duomenys nespėja patekti iki atminties registrų. 🙂

Labai įdomios mikroschemos, tačiau jos buvo nepopuliarios megėjiškame pasaulyje nes jos buvo baisiai brangios ir nebuvo free softo. Laikai keičiasi- mikroschemos pinga ir labai tobulėja. O softas nemokamas ir dar yra daug freewarinių softcore dalykėlių.

Mane “inspiravo” FPGA nagrinėjimui http://www.fpga4fun.com/ puslapis. Rekomenduoju pasiskaityti.

patikek manim tikrai ko daug nezinau :d bet noris suzonot todel ir kyla klausimu

Nusipirkom BGA resoldering station, 15k Lt mokejom, su pozicionavimo sistema per atskira monitoriu, tai pagaliau prasides normalus darbas su BGA :)) Idomu butu koki logini analizatoriu uzkurt… Tiesa, dar kas keista… Jei Xilinx su Spartan giriasi 500k geitu, tai cia “tik” 48k ? Kodel toks kontrastas?

taigi čia šrotas >10 metų senumo. 🙂

Pozicionavimas tai gal ir gerai, bet kas PIGIAI padarys PCB skirta BGA čipams?

Kinai? 🙂 Padaryt tai padarys, bet kas Lietuvoj normalia plokste sutrasuos? 🙂

aš kalbu apie megėjiškas plokštes. Tikrai norėčiau kur nors pigiai darytis 2 ar daugiau sluoksnių plokštes su teisingu apsauginiu sluoksniu ir silk screenu… Pasižiūri į “buržujų megėjų” plokštes tai net širdį suspauždžia- koks nors niekalas, o viskas padaryta fabrikėlyje. Gerai jiems, jie daug uždirba ir ne Marijos žemėje gyvena.

O http://www.telga.lt negaletu padaryt prototipo? 🙂

Nu jei Lietuvaičiai nusileido iš kosmoso, tai gal ir padarytu. Bet manau, jie su megėjais nesusideda arba kaina gausis didesnė nei kinų. Ar tik nebus kaip su kitais Litowcais, kaina gal ir nieko, bet prasideda visokie paruošimo mokesčiai ir panašiai… 🙁 Sumoje, kinai dvigubai pigiau padarytu ir dar dovanų duotu.

Telga ne tik kad daug lupa, bet dar ir labai shudinai padaro. Tikrai nepatariu ten ploksciu su smulkiais koju tarpais daryt 🙂

Kam tos zamarochkes megejui su BGA, jei nori perki Devboard’a kaip AVNET SPARTAN 3A 400k Evolution kit uzh 49$ + siuntimas + mokeschiai. Pirkau 2008 priesh krize buvo uzh 39$ = 150 Lietuvishku litu su visom ishlaidom, gavau Spartan 3A 400k FPGA, Cypress PSOC, “capacitive touch” ir temperaturos sensoriu, originalu Cypress PSOC Mini Prog ir ketursluoksne PCB plokshte su pilna gamintojo dokumentacija. Nu db pamegink visa tai pasidaryti pats, taigi kosmosas gausis, tiek laiko – tiek pinigu atzvilgiu. Dar yra panashus kitas ish Latice uzh varganus 49$ nepamenu modelio… Ant FPGA devboard’o yra I/O headeriai prie kuriu jungi savo suprojektuota periferija gali darkytis kaip nori…

Devboardas yra gerai kai nori paeksperimentuoti. O kai nori kažką savo ir tada viskas. Turiu aš kelis devboardus- du padėti giliai į stalčių, vienas (DE1) kartas nuo karto paklibinamas. O štai savadarbiai tikrai panaudojami. Ir kai vienam savadarbiui pystelėjau 12V per kojas, tai užteko užkelti naują šrotinį ir viskas čiki.

Nu sudominai čia mus, Levai, dabar turėsi rašyt postą “FPGA žaliems”. 🙂 Na ir fpga4fun reiks perskaityt, kai bus laiko. Gera nuoroda..

Nepakibkit su tuo fpga4fun, ne viskas ten veikia 😉 Ir siaip, sunku apsisprest ar Verilog geriau mokintis, ar VHDL 🙂

A kartais ne TEO dirbi/dirbai?

Niekada gyvenime. 🙂 Tokį šlamštą telekomas parduoda viešų aukcionų metu.

Idomu tiktai, kas toki slamsta superka. O be to, kas dabar slamstas, seniau kainavo didelius pinigus.

Dabar irgi ne centus kainuoja. Tikrai gautum 20Lt už kilogramą 🙂