Čia straipsniukas tikriausiai ne apie kažkokią šviesos diodų matricą, bet labiau apie vieną iš technologijų kurią naudoju kai reikia padaryti “reverse engineering”.

Labai dažnai kokie nors senesni prietaisai ar šiuolaikinė Kiniška elektronika neturi jokios dokumentacijos. Matyt arba duomenys labai seni arba Kinai per savo bjaurų charakterį neviešina informacijos. Tačiau kartais norisi pasinaudoti esamais blokais, elementais ar prietaisais. Tačiau kaip? Informacijos nulis!

Pirmiausia apžiūrim ir nustatom kur yra žemė ir kur maitinimas. Pagal žinomas detales pabandom atspėti kiek voltų įtampos reikia paduoti. Visada naudojam kiek galima mažiau ir ribojam srovę. Vėliau bandom atspėti kur yra įėjimai, o kur išėjimai. O toliau prasideda mistika ir “метод научного тыка”.

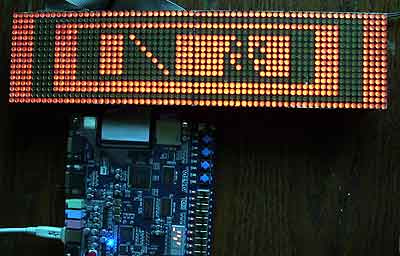

Gyvas pavyzdys. “Berniukai” iš sandėlio parūpino kažkokią raudonų šviesos diodų matricų bloką. Jis atrodo taip, tiesa jis dar nešvietė. Tai 64 x 16 LED matrica iš Taito Corporation kažkokio žaidimų automato. Beja, ši firma sukūrė klasikinius Space Invaders. 🙂

Kiek pasinagrinėjus buvo nustatyta, kad visa matrica naudoja 5V matinimą. Tai buvo nustatyta pastebėjus, kad prie pagrindinių Vcc it GND laidų pajungta mikroschemos MC74HC04AN, AM26LS32, TD62C962 ir t.t. Jų maitinimų artimiausias standartinis bendras vardiklis- 5V.

Valdymas pajungtas prie jungties prie kurios prilituotos dvi 26LS32. Tai RS485 lygio keitikliai. Pagal PCB matosi, kad naudojami 8 laidininkai ir visi eina į matricą. Iš matricos signalų nerasta.

Bandant ieškoti Toshibos TD62C962LF mikroschemos aprašo nieko gero nerasta. Tik nustatyta, kad panašios mikroschemos naudojamos printerių termo galvom, keliems LED draiveriams. Bet nieko konkretaus.

Takelių treisinimas privedė, kad pora valdymo signalų eina tik į MC74HC161 (4-bit binary counter) ir MC74HC4514 (4-to-16 line decoder/demultiplexer) čipus. Tai kažkas panašaus į matricos eilučių skaitliuką ir dekoderį. Taip atsirado pradinė informacija. Tačiau likę 6 laidai sulindo į Tošibos krakajobą…

O štai čia išlenda “reverse engineeringas” pagal “метод научного тыка”. Rusiškai nesuprantantiems ar tiems kurie nežino šio išsireiškimo: spaudžiojimas bet kur ir laukiant kažkokio rezultato.

Šiam reikalui galima pasinaudoti paprasčiausius perjungiklius (bent jau pradžiai). Tačiau žymiai įdomiau (ir paskutiniuose etapuose patogiau) pasinaudoti ką nors protingesnio. Tam tinka personalinis kompiuteris, mikrokontroleris arba CPLD/FPGA. Visi metodai turi savo pliusų ir minusų. Šiam konkrečiam projektui pasirinkau FPGA dev boardą, nes pirmiausia čia viskas sumontuota ir yra mygtukai, o antriausia- esamas softas labai galingas ir lankstus. Ypač padeda simuliacijos ir diagramų paišymas. Dar vienas FPGA pliusas, kad signalų greitis nėra ribojamas kompo ar MCU našumu. Čia dešimtys megahercų yra visiškas niekutis.

Nesigylinsiu į tai kiek buvo padaryta pakeitimų ir spėjimų. Tačiau parodysiu koks turi būti galutinis signalas į matricą:

Paaiškėjo, kad 4 bitai eina tik į LEDų grupę. T.y. matrica priima po 4 taškus per vieną taktinio laikrodžio impulsą. Todėl į šią diagramą tai neįtraukta. Tačiau matosi kaip skaičiuojasi matricos video atminties adresas.

Po daugybės nesėkmių buvo nustatyta, kad row_clock atlieka dvigubą vaidmenį- perjungia naudojamą matricos eilutę ir kartu užžiebia diodus (enable).

Visą šitą velniavą suformuoja šios kelios Verilog kalbos eilutės:

/* Taito K9100427B, J9100320B LED PCB reverse engineering test This is 64x16 (Total 256 LEDs) board. Original connection 8 differencial RS485 lines. Serial data transfer, 4 LEDs at clock. Data to board: row_clock, row_reset, column_clock, column_reset, d0-d3 Verilog module input: master clock (tested 5MHz), reset Additional module outpur: Video RAM address. (c)2010 by Savel. http://www.vabolis.lt */ module advanced (clock, reset, row_clock, row_reset, column_clock, column_reset, ram_adr); input clock, reset; output reg row_clock, row_reset, column_reset,column_clock; output [7:0]ram_adr; reg [11:0]state; reg [3:0]eilute; reg [3:0]x; reg fclock; assign ram_adr[3:0]=x[3:0]; assign ram_adr[7:4]=eilute[3:0]+1; always @(posedge clock) begin fclock<=~fclock; end always @(posedge fclock) begin if (reset==0) state<=state+1; else state<=0; end always @(posedge clock) begin if (state[7:0]>=8'h01 && state[7:0]<8'h20) begin column_clock<=state[0]; end else begin column_clock<=0; end if(state[7:0]>=8'h00 && state[7:0]<8'h02) column_reset<=1; else column_reset<=0; if(state[7:0]>8'h21 && state[7:0]<8'hFC) row_clock<=1; else row_clock<=0; if(eilute==8'h00 && state[7:0]>=8'h00 & state[7:0]<8'h0f) row_reset<=1; else row_reset<=0; end always @(posedge row_clock) begin if (reset==0) eilute<=eilute+8'h01; else eilute<=0; end always @(negedge column_clock) begin x<=x+1; end endmodule

Šis kodas nėra nei optimalus nei labai jau moksliškas. Tačiau būtent šiuo kodu buvo “atrakinta” matrica. Žinant reikiamus parametrus, Verilog kodą galima parašyti žymiai taisyklingiau.

Dabar, kai žinoma kas ir kaip jungiasi. Galima galvoti apie praktišką matricos panaudojimą. Dabar jau nebereikia FPGA, darbą gali atlikti ir bet koks nedidelis mikrokontroleris.

P.S. Ruošiant įliustracijas fotikas parodė, kad dar yra kažkokia taimingo problema:

Kažkoks šėšėliavimas žemyn. Matyt eilutės persijungia kiek greičiau nei spėja užgesti.

…

Perdarius sistemą į MCU versiją su ATMEGA16, greitis stipriai nukrito ir šėšėliavimas dingo. Matyt su FPGA bandymais kiek užlenkiau dažnį.

Blemba blemba, kiek čia reikia smegenų, kad tokius biliburdą iššifruotum ir suprogramintum 🙂 Šaunuolis. Man tai čia beveik paukščių kalba atrodo 😀

Smegenu pas visus vienodai, tik va ne visi jas panaudojam tinkamai.. 😀

pas jį truputį daugiau nei pas kitus 😉

Baikit šnekėt apie mano smegenų kiekį. Nejaukiai jaučiuos. Manau kiekis standartinis, bet kiek pakeistas į vieną šoną, nes pastebiu pas save kai kurių dalykų trukumus 🙂 Matyt elektronika užpildė neteisingas spragas.

vistiek pagarba ! 🙂

Sudėtingai, nice 🙂

Kas liecia fotika as galvos neguldyciau, nes fotkes metu o ypac tamsiu fonu uzlaikimas didelis, gali pagauti stipriai svieciancius objektus keliuose kadruose. Cia fotografai tau pasakys kaip vieno kadro metu vienas zmogus gali atsirasti trijose vietose kolektyvineje nuotraukoje 🙂 . Geras darbas

[…] seniai rašiau apie raudonų šviesos diodų matricą. Šiaip programa nedadaryta iki galo, bet kadangi ji funcionali ir veikianti, tai […]