Šį straipsniuką prašė parašyti “Miltukų Meistras”.

Jei netyčia nusipirkot išorinį LG slim DVD RW įrenginį (GSA-E50L, HL Data Storage Inc. Hitachi-LG) ir staiga jis nustojo veikti ir baigėsi garantinis, nepulkit į paniką. Gal tai tipinis šio modelio gedimas- tikriausiai programinė problema.

Paciento simptomai: įjungus maitinimą užsidega žalias šviesos diodas. Tačiau kompas nemato jokio įrenginio ant USB laido. Taip pat neveikia atsidarymo mygtukas.

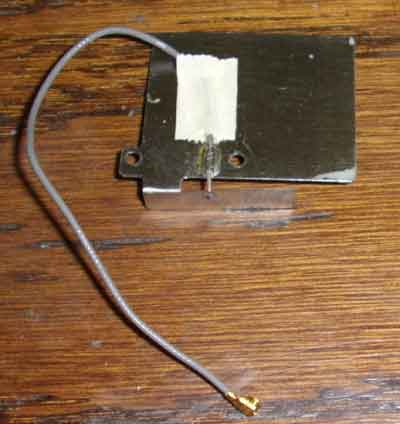

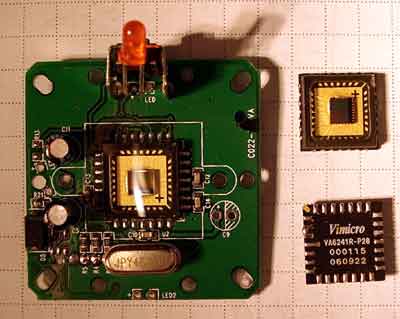

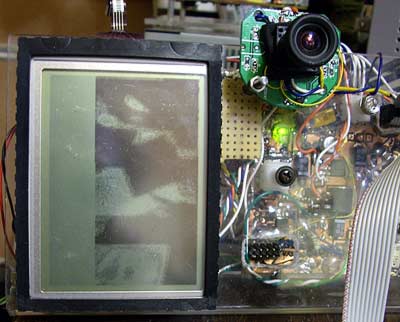

Remontas labai paprastas- naudodami mažą kryžminį atsuktuvą atsukam 6 varžtus. Atsidarom dėžutę. Viduje atsukam dar vieną varžtelį ir atlaisvinam patį DVD-RW įrenginį. Turim rankose turėti nedidelę spausdintą plokštę (PCB) ir patį DVDRW. Dabar pats remonto metodas. Įjungiam į kompą USB laidą (įšorinio maitblokio nereikia) ir veikiančiam aparate atjungiam ir vėl prijungiam jungtį tarp PCB ir DVDROM. Po šio eksperimento turi pradėti mirksėti šviesos diodas ir viduje įrenginio sušvisti lazeris ir sujudėti galva.

Viską gražiai susukam atgal ir sėkmingai naudojam aparačiuką. 🙂

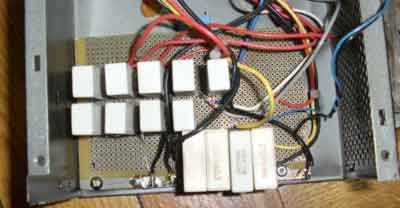

Žingeidiems- ardydami aparatą atkreipkit dėmesi į keistą kondensatorių kuris pavadintas “Energy storage, 5V 0.5F”. Tas stebūklas padarytas iš dviejų faradinių kondesnatorių po 2.5V sujungtu nuosekliai. Šis kondikas pajungtas tiesiogiai prie 5V šynos. Tikriausiai kaupią energiją įrašymo metu- taip galima naudoti žymiai mažesnio galingumo maitblokį ar netgi naudotis tik USB laido maitinimu.