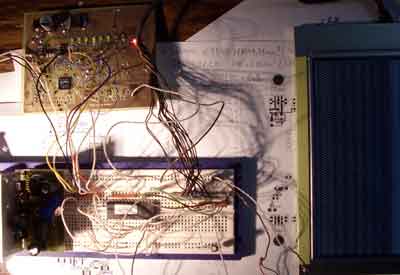

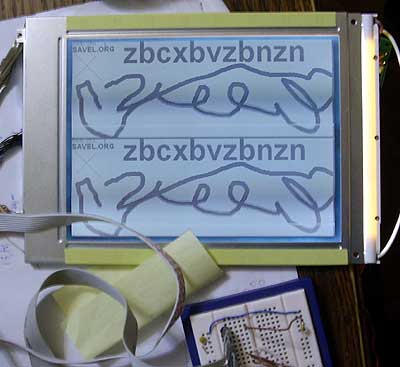

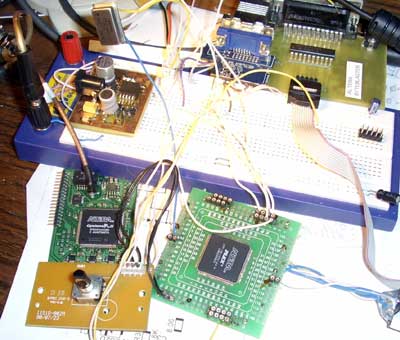

Va norėjau jums parašyti daugiau apie FPGA mikroschemas, dariau jums veikianti modelį ir dėl mano išsiblaškymo susvilinau mano Altera Flex čipuką. Man darbo laukas lygtai ir nebuvo labai sudėtingas. Buvau jau sukonstravęs veikianti modulį ir norėjau kiek patobulinti… Va darbo lauko fotkė:

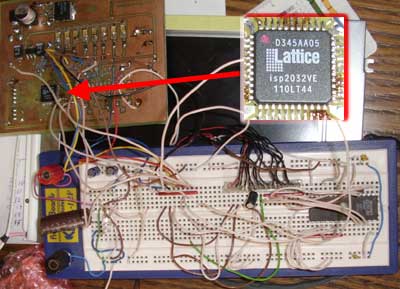

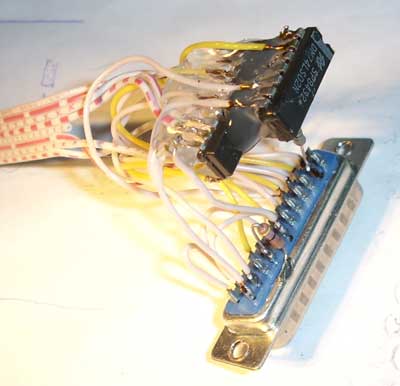

Čia matosi maketinė ploštė su maitinimo šaltiniu, ByteblasteMV programavimo kabelis, Altera Flex maketinė plokštė su EPF10K10TC144-4 čipuku (iš tikruju čipukas prilituotas prie universalios plokštės iš Lemonos- 15Lt), rotary encoderis (sukinėji rankenėle ir jis generuoja impulsus pasislinkusia faze), Altera Cyclone II (EP2C5T144C6N)- šitas čia jau kaip pakaitinis, dar neišbandytas ir dar matosi VGA kištuko adapteris maketinei plokštei su pajungtu CRT VGA monitorium.

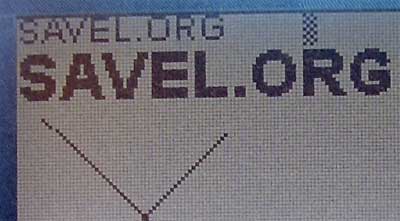

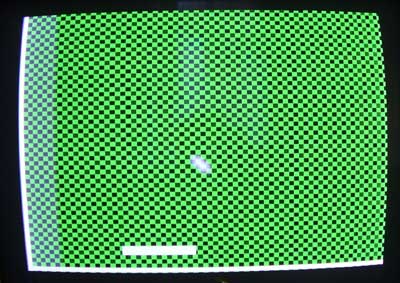

Visa šita mašinerija sugeneravo va tokį vaizdelį ant VGA monitoriaus:

Čia aš nieko pats neišradau, viskas nukopijuota iš interneto, tik kiek pakeisti parametrai, kad prisitaikyti prie mano turimos hardware ir mano naudoto osciliatoriaus. Deja niekaip nepavyko priderinti VGA dažnių kad matytusi visas teisingas vaizdas. Tas kliaksas per vidurį ekrano tai judantis kvadratėlis kuris atsimuša nuo sienelių ir nuo “raketėlės”. Pastarąją galima stumdyti į šonus sukinėjant encoderį.

Taigi norėjau visą šitą sistemą perkelti iš CRT VGA monitoriaus į LCD panelę. Tačiau netyčia pajungiau encoderį ne prie žemės, o prie LCD bias (~ -15… -20V) ir mano vargšas FPGA sudegė. Sudegė vienas I/O blokas ir čipukas labai kaista. Ir aišku nebesiprogramuoja, nes prieš programavimą atliekama diagnostika. Nors CORE dar veikia- galima nuskaityti, kad čipukas dar kabo ant JTAG grandinės.

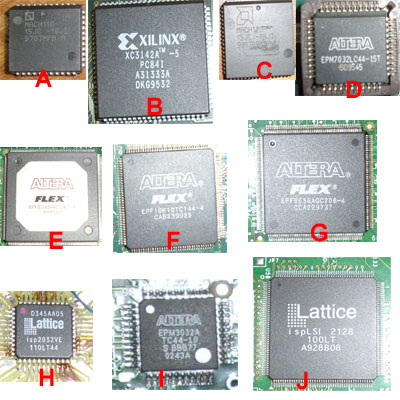

Kol kas teks jums apseiti be detalaus aprašymo. Nes kito tokio pat FPGA neradau. Nupirkau aš porelę eBay aukcione, bet kol jos pas mane atsiras. O su Cyclone II dar nepradėjau žaisti- čia parinkta iš vienos Lietuvos firmos broko. Net nežinau ar jos veikiančios. Reikia man pasidaryti 3.3V ir galbūt 1.2V (core) maitblokius. Ir nėra garantiju, kad nors vienas ciklonas bus veikiantis- nors kai kurie labai baisiai prilituoti ir lydmetalis patekęs tarp kojyčių.