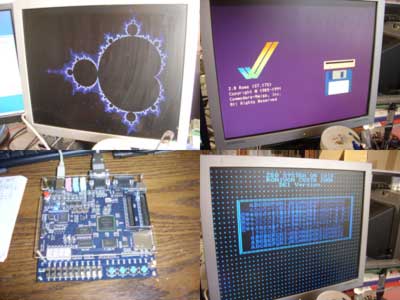

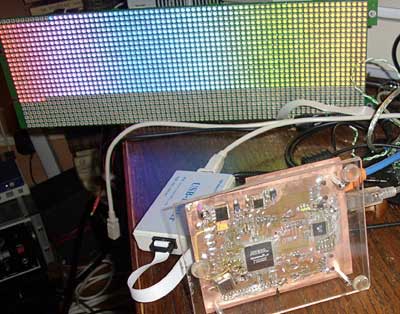

Vėl prisiminiau savo žaidimus su FPGA čipu. Prisiverčiau pasižaisti su virtualiu (softcore) procesorium. Juolab, kad Altera atidarė savo licenziją ir NiosIIe procesorių galima naudoti savo kūriniams nemokamai. NiosIIe procesorius tai 32 gyvis su galimybe prikomponuoti matematinį koprocesorių (FPU).

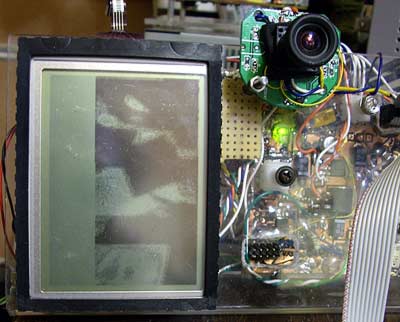

Procesorių nutariau sukišti į savo gamybos plokštę su minimaliu Cyclone II čipu (EP2C5T144). Kas įdomiausia, softas su programiškai padaryta slankiojo kablelio matematika netilpo į čipo vidinę atmintį, tačiau tilp FPU ir softas su koprocesoriaus panaudojimu :).

Kad palyginti procesoriaus greitį, panaudojau tą patį softą (C kalboje) tiek ant Atmega 16, tiek ir su NiosII procesorium. Štai jumi ir rezultatas:

Pagrindiniai parametrai:

- ATMEGA16, veikianti 12MHz dažniu. Softas kompiliuotas su GNU C. Interfeisas su FPGA čipu per 4 duomenų bitus ir keliais kontroliniais laideliais. FPGA vidinis skaitliukas resetinamas su Atmega, vėliau paveiksliukas pumpuojamas po 4 bitus. (4 bitai, strobas, 4 bitai, strobas, FPGA padidina adresą, ir taip ratu).

- NiosIIe, ekonominis, nemokamos licenzijos procesorius. Softas kogero irgi GNU C kompiliuojamas. Duomenų perdavimas kiek kitoks, nes viduje FPGA sujungti žymiai lengviau: 8 bitai duomenim, kelioliką bitų adresui. Kaip jau ninėjau- FPU, hardware floating point (sudėtis, atimtis ir daugyba). Procesorius veikia nuo 50MHz taktinio dažnio. Didesnio dažnio negalėjau panaudoti, nes FPGA neturi laisvo PLLo (PLLas naudojamas LVDS interfeisui).

- NiosIIf, tas pats kaip ir NiosIIe, tik dabar “komercinė” versija, vadinama dar “fast”. Matosi, kad kiek greitesnė. Tačiau pagrindinis greitumas pasijaustu, jei softas važiuotu iš išorinės SDRAM ar DDR atminties.

Tikėjausi žymiai didesnio greičio skirtumo. Gi Mega tik 8 bitų, neturi “geležinio” slankiojo kablelio ir važiuoja nuo 12MHz (todėl, kad toks kvarcas prilituotas). Tuo tarpu Niosas 32 bitų, hardwarinis floating point, groja ant 50MHz ir naudoja vidinę FPGA atmintį kuri tikrai nestabdo.

Nemanau, kad reikia publikuoti softą (tiek C, tiek Verilog) nes hardwarė labai jau specifinė ir niekas jos nepasidarys. Jei labai labai susidominot, rašytik laiškelį, pamačysim.