Iš eilės einantys skaičiai nelabai įdomūs. Todėl prie mūsų “video kontrolerio” reikia pritaikyti atmintį. Kad į tą atmintį rašyti informaciją, o displėjus rodytu kas ir kaip čia gaunasi.

Maždaug taip:

Čia dar galima pastebėti, kad aš padidinau šrifta du kartus tiek į plotį, tiek į aukštį. Paprasčiausiai labai jau mažos raidelės buvo ant ekrano, o ir video atmintis labai didelė gautusi. Continue reading →

Category Archives: FPGA/CPLD

FPGA:0006 – VGA Taimingo tiuninimas

Rašiau, kad eksperimentiniame SVGA displėjuje raidelės nesutampa su fonų ir minėjau, kad bandysim tai remontuoti.

Pirmiausia, reikia visus signalus- ir teksto ir fono, ir gal kokių nors spraitų spalvinę informaciją sinchronizuoti su pixel clocku. Tam tikslui esame “blankerio” modulį perdarom iš paprastos logikos į sinchroninį, naudojantį registrus. Naujas source kodas jau atrodo taip:

module blanker(clk,r,g,b,blank,qr,qg,qb); input clk; input [3:0] r; input [3:0] g; input [3:0] b; input blank; output reg [3:0]qr; output reg [3:0]qg; output reg [3:0]qb; always @(posedge clk) begin qr <= (blank) ? 8'b00000000 : r ; qg <= (blank) ? 8'b00000000 : g ; qb <= (blank) ? 8'b00000000 : b ; end endmodule

FPGA:0005 – Tekstinis displėjus

Papaišėm spalvotus fonus. Bet jei norime parodyti kokį nors tekstą, panašiai kaip senoviniam tekstiniam displėjuje? Aišku galima! Viena iš pirmųjų minčių- prikabinti didelį video RAMą kaip šiuolaikinėse video plokštėse ir nuo RAM turinio keisti vaizdą. Aišku taip galima, bet mes neturim tiek atminties. Netgi naudojant po 4 bitus vienai spalvai, gaunasi: 1024x768x3x4/8=1179648 baitai (1.125 megabaito). Tačiau mums užtenka tekstinio displėjaus. Jį sudaro tekstinė atmintis, šrifto atmintis ir spalvų atmintis (kartais paletizuota). Kadangi tingiu paišyti ir ieškoti internete, panaudosiu 8 bitų ATARI kompiuterio šriftą, kurį savo laiku ištraukiau iš to kompo ROMo. Šis šriftas skirtas TV ekranui, todėl jis toks pastorintas. Šriftas užima 8×8 matricą, tačiau iš šonų visada yra tušti pixeliai raidžių atskirimui. Senoviški ekranai naudodavo mažesnes matricas, o tarpelius tarp raidžių darydavo hardwariškai. Gal apseisim be šito.

Continue reading →

FPGA:0004 – SVGA

Pažaidus su LEDais, pabandykime prijungti kokį nors VGA monitorių. Kadangi mano eksperimentinis monitorius yra LCD su 1024×768 raiška, tai man reikia susigeneruoti tokią “video plokštę” kuri palaikytu tokią rezoliuciją. kodėl tiksliai pataikyti į “native resolution”? Ogi kad pažaisti su smulkiais objektais ir taimingais.

Iš senesnio mano puslapio galima sužinoti standartizuotus VESA taimingus ir video generavimo koncepcija. Internete pilna visokių video generavimo schemų ir variantų, tačiau aš naudosiu savo. Bent jau aiškinimuose kaip veikia. Pirmiausia reikia susikonstruoti VGA kištuko “šieldą” arba “add-oną”. Kadangi ateityje norėsiu pabandyti daugiau spalvų, tai nutariaus sulituoti 4 bitų DACą kiekvienai spalvai. Tai duos iš viso 4096 spalvas. Tiek pat, kiek sugebėjo rodyti pirmieji Amiga kompiuterio modeliai.

Kiekvienas save gerbiantis VGA monitorius turi 75 omų apkrova savo viduje, o maksimalaus raiškio įtampa kažkur apie 0.7V (700mV). Mūsų “video plokštė” turi tik 3.3V LVTTL išėjimus, ir rodos max 20mA per koją (su apribojimu visam blokui ir čipui). Todėl reikia pasidaryti patį primytyviausią DACą (digital analog converter). Tam reikes apie 0.5k, 1k, 2k ir 4k rezistorių. Kadangi tokie tiksliai rezistoriai neegzistuoja (ypač mano stalčiuje), tai pasirinkau: 512R, 1K, 2K, 3.4K. Kiek paskaičiavus ir gaunasi, kad įtampa spalvos laide svyruos nuo 0 iki maždaug 700mV. O kaitaliojant bitus įtampa keisis maždaug tiesiškai. Beja tą ir parodė vėliau osciloskopas.

Continue reading →

FPGA:0003 – LEDai

Garsą jau turim, dabar biški vaizdo. Yra 3 LED ant tos plokštės sujungti per rezistorių prie Vcc. Pas mano plokštę jie pažymėti kaip D2, D4 ir D5. Aš čia prilitavau skirtingų spalvų LEDus: raudoną, žalią ir mėlyną. O kad dar krūčiau būtų, maitinimo pajungimo indikacijos LEDą D3 padariau baltos spalvos. 🙂

Su FPGA uždegti LEDą galima taip pat, kaip ir mikrokontroleryje- užtenka atitinkamą koją perjunti į žemę (nes LEDas į Vcc) ir LEDai dega. Tiesa jie dega ir dabar, nes nenaudojamos kojos užsiprogramuoja į žemę.

Jei norime, kad LEDas mirksėtu užtenka pagrindinį 50MHz clocką pasidalinti iki kelių hercų ir paduoti į LEDą. Ir jis mirksės.

Continue reading →

FPGA:0002 – Cypukas

Kai jau kažkas suveikė ir signalas perėjo iš vieno mikroschemos šono į kitą, reikia tą signalą kaip nors modifikuoti.

Aišku galima iš bibliotekos prisidėlioti visokių loginių elementų į schemos puslapį ir viskas veiks. Bet mūsų užduotis pasigaminti modulį kuris veiks pagal mūsų norus. Ką nors nestandartinio.

Tačiau pradžiai reikia pasidaryti pirmą periferinį įrenginį- mažyčiuką garsiakalbiuką. Aišku nesamonė jungti tiesiogiai garsiakalbiuką prie LVTTL kojos, reikėtų kokio nors buferio, tačiau bus gerai ir tiesiogiai. Aš panaudojau cypuką iš kompų motininės plokštės. Kad netrumpinti FPGA kojos, nuosekliai įlitajau nedidelį rezistorių- kad srovė neviršytu leistinos mikroschemos išėjime.

Mūsų FPGA turi vienintelį CLK šaltinį 50MHz osciliatorių (25MHz gal pas ką nors). Tokio dažnio tikrai niekas negirdi, nebent radio imtuvai. Todėl dažnį reikia sumažinti. Lengviausia tai padaryti su skaitliuku.

Continue reading →

FPGA:0001 – Softas, konfiguravimas, pirmas paleidimas

Straipsnis tikrai atsirado greičiau nei koks nors skaitytojas įsigijo dev boardą. Tačiau softą dalinai galima pasibandyti.

Paleidus Quartus programą spaudžiam naujo projekto darymo “wizardą”. Spaudžiam NEXT ir pasirenkame direktorija kurioje kursime savo pirmą projektą. Darbo metu ten susikurs melionas ir dar biški failiukų, todėl reikia susikurti naują direktoriją. Pasirenkam projekto pavadinimą, kad ir “FPGA001”. NEXT.

Čia galima pridėti esamus failus prie projekto. Nieko dar neturim, tai spaudžiam NEXT.

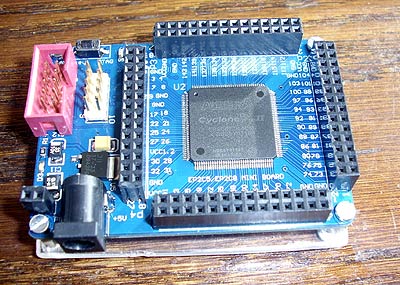

Dabar pasirenkam kokią mikroschemą naudosim. Čia jau kokią prisilitavot, nusipirkot, tą ir pasirinkit. Aš renkuosi Cyclone II šeimą, 144 kojos, EP2C8T144C8. Čia pamatom, kad šitas čipas turi 1.2V core maitinimą, 8256 loginius elementus, 85 vartotojui panaudojamas kojas, 165888 atminties bitus, 36 loginio dauginimo elementus, 2 PLLus ir 8 globalius CLK sujungimus. NEXT

EDA tool settings nesvarbu kol kas. NEXT. FINISH.

Continue reading →

FPGA:0000 – Intro

Labai mažai rašiau FPGA/CPLD temoje, o ir tautinėje “spaudoje” ši tema mažai apšviesta. Todėl (nes išsibaigė fantazija) nutariau parašyti keletą straipsnių apie FPGA čipus ir jų panaudojima. Aišku, stipriai remsiuosi FPGA4FUN puslapiais. Gal net plagijuosiu. Ir dar, nesiruošiu apibrėžti visko ir visada. Todėl mano pasakojimui bus apie Alteros produktus ir verilog kalbą. Kitų neįvaldžiau.

Kadangi žaisti su FPGA “sausai” yra didelė nesamonė, o pramoniniai dev-boardai karvę kainuoja, tai pradedu pasakojima apie pigų dev boardą.

(Altera Cyclone II, EP2C8T144C8N)

Tokių dev boardų su Altera Cyclone II (EP2C5 arba EP2C8) pilna eBay. Yra plokščių, kur viskas sulituota (rodos apie 20…30$ kainuoja), o yra tik PCB (~3$ su atsiuntimu).

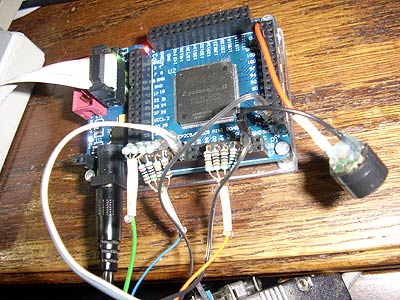

Jei rankos nekreivos, turite kur nors laisvą FGPA ciklono čipą, tai galima pačiam prisilituoti. Aš taip ir padariau (čipas iš seno LCD teliko). Taip pat prilitavau konfiguracinį flešiuką (nebūtina) ir kitas aprišimo detales (3.3V ir 1.25V stabilizatorius, 10K rezistoriai, keletas mažų kondikų, keli LEDai, 50MHz osciliatorių). Sulitavau JTAG ir serial prom programavimo jungtis.

Dar reikia įsigyti programavimo kabelį (pats primityviausias prie LPT porto netgi lengvai pasidaromas). Rekomenduočiau patį paprasčiausia USB Byte blasterį.

Continue reading →

Loginis analizatorius

Viena iš komentarų buvo rašyta apie USB oscilografus ir loginius analizatorius. Klausė ar aš bandžiau… Deja nebandžiau. Tačiau jau seniai masčiau ne apie USB oscilografą, bet loginį analizatorių. Bandžiau net FPGA versiją, ten viskas veikė, tačiau pagrindinė bėda su tais analizatoriais yra softas. Tiksliau jo nebuvimas. Jau keletą metų anksčiau žiūrėjau į USBee projektą. Tačiau legalus variantas labai jau brangus. Tačiau laikai keičiasi, negeri kiniečiai nukopijavo hardwarą ir padarė veikianti su softu. Dar jie padarė ir softo nulaužimą… labai jau negražu. Tačiau dėl kelių pažaidimų mokėti šimtus aš nenorėjau (brangiau už mano oscilografą!), o štai sumokėti $40 jau galiu. Taigi, per pora savaičių ant stalo atsirado toks daiGtas:

(USB laidas nepajungtas)

Komplekte tokie čiuptuvėliai:

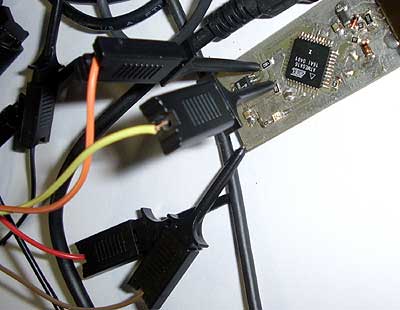

Pirmiausia, kapitalistai pradėjo kovoti su kinais, tai jei netyčia gausit tokį prietaisą pasiruoškit jį perdaryti:

Čia yra USB VID/PID atminties mikroschema. Originalus naujas softas mėgsta naikinti šiuos VID/PID. Gal originaliam hardware ši mikroschema apsaugota nuo įrašymo. Tuo tarpu Kinai padarė perrašoma- taip galima padaryti ne tik USBee įrenginį, bet ir persiklonuoti į kitą komercinį projektą (jau užmiršau pavadinimą). Tereikia tik perrašyti VID/PID. Man užteko tik USBee, tai paprasčiausiai užtenka write protect koją sujungti su Vcc. WP koja atkelta nuo PCB ir su lydmetalio lašu sujungta su Vcc.

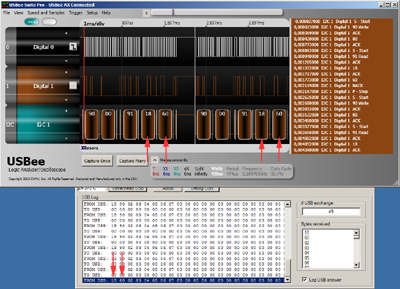

Nu ir softo screenšotas:

(pasidinina)

Softas analizuoja kelis protokolus, yra analoginis osciloskopas. Gali dirbti kaip generatorius ir t.t. Paprasčiausiai, šias funkcijas aš neišbandžiau. Nelabai buvo jos reikalingos man. Tačiau man reikėjo I2C analizės. Paveiksliuke paprasčiausias I2C variantas, čia nuskaitymas iš LM75/FM75 mikroschemos, mano senas USB termometro projektas. Matosi apačioje USB debug langas ir tie patys skaičiai.

Tikiuosi, kad dar ką nors parašysiu apie šį gaminį. Tačiau dabar kažkaip laikas spaudžia ir nėra projektų. Tiesiog kurybinė ir laiko krizė 🙁

Raudonų šviesos diodų matrica

Čia straipsniukas tikriausiai ne apie kažkokią šviesos diodų matricą, bet labiau apie vieną iš technologijų kurią naudoju kai reikia padaryti “reverse engineering”.

Labai dažnai kokie nors senesni prietaisai ar šiuolaikinė Kiniška elektronika neturi jokios dokumentacijos. Matyt arba duomenys labai seni arba Kinai per savo bjaurų charakterį neviešina informacijos. Tačiau kartais norisi pasinaudoti esamais blokais, elementais ar prietaisais. Tačiau kaip? Informacijos nulis!

Pirmiausia apžiūrim ir nustatom kur yra žemė ir kur maitinimas. Pagal žinomas detales pabandom atspėti kiek voltų įtampos reikia paduoti. Visada naudojam kiek galima mažiau ir ribojam srovę. Vėliau bandom atspėti kur yra įėjimai, o kur išėjimai. O toliau prasideda mistika ir “метод научного тыка”.

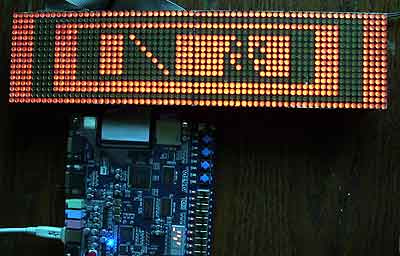

Gyvas pavyzdys. “Berniukai” iš sandėlio parūpino kažkokią raudonų šviesos diodų matricų bloką. Jis atrodo taip, tiesa jis dar nešvietė. Tai 64 x 16 LED matrica iš Taito Corporation kažkokio žaidimų automato. Beja, ši firma sukūrė klasikinius Space Invaders. 🙂

Kiek pasinagrinėjus buvo nustatyta, kad visa matrica naudoja 5V matinimą. Tai buvo nustatyta pastebėjus, kad prie pagrindinių Vcc it GND laidų pajungta mikroschemos MC74HC04AN, AM26LS32, TD62C962 ir t.t. Jų maitinimų artimiausias standartinis bendras vardiklis- 5V.

Valdymas pajungtas prie jungties prie kurios prilituotos dvi 26LS32. Tai RS485 lygio keitikliai. Pagal PCB matosi, kad naudojami 8 laidininkai ir visi eina į matricą. Iš matricos signalų nerasta.

Bandant ieškoti Toshibos TD62C962LF mikroschemos aprašo nieko gero nerasta. Tik nustatyta, kad panašios mikroschemos naudojamos printerių termo galvom, keliems LED draiveriams. Bet nieko konkretaus.

Takelių treisinimas privedė, kad pora valdymo signalų eina tik į MC74HC161 (4-bit binary counter) ir MC74HC4514 (4-to-16 line decoder/demultiplexer) čipus. Tai kažkas panašaus į matricos eilučių skaitliuką ir dekoderį. Taip atsirado pradinė informacija. Tačiau likę 6 laidai sulindo į Tošibos krakajobą…

O štai čia išlenda “reverse engineeringas” pagal “метод научного тыка”. Rusiškai nesuprantantiems ar tiems kurie nežino šio išsireiškimo: spaudžiojimas bet kur ir laukiant kažkokio rezultato.

Šiam reikalui galima pasinaudoti paprasčiausius perjungiklius (bent jau pradžiai). Tačiau žymiai įdomiau (ir paskutiniuose etapuose patogiau) pasinaudoti ką nors protingesnio. Tam tinka personalinis kompiuteris, mikrokontroleris arba CPLD/FPGA. Visi metodai turi savo pliusų ir minusų. Šiam konkrečiam projektui pasirinkau FPGA dev boardą, nes pirmiausia čia viskas sumontuota ir yra mygtukai, o antriausia- esamas softas labai galingas ir lankstus. Ypač padeda simuliacijos ir diagramų paišymas. Dar vienas FPGA pliusas, kad signalų greitis nėra ribojamas kompo ar MCU našumu. Čia dešimtys megahercų yra visiškas niekutis. Continue reading →