Vienas labai patogus prietaisiukas kurio dažnai prisireikia yra daugiakanalis loginis analizatorius. Tai prietaisiukas kuris greitai surenka duomenis iš keletos/keliolika/keliasdešimt kanalų ir leidžia kompiuterio pagalba analizuotis kaip ten kas veikia. Bėda tame, kad prietaisai keičiasi duomenim labai sparčiai ir paprastom priemonėm šios informacijos pagauti ir persiusti į kompiuterį neimanoma. Tokie prietaisiukai daromi kiek sudėtingiau: iš pradžių duomenys nuskaitomi su įvairiom mikroschemom į kokią nors atmintį, o vėliau, žymiai lėtesniais metodais perduodami į kompiuterį tolimesnei analizei. Protingesni loginiai analizatoriai dar sugeba pradėti registruoti duomenis nuo kažkokios signalų kombinacijos, naudodami taip vadinama trigerį. Nes kartais labai sunku pagauti reikiamą signalo pradžią.

Toki prietaisiuką megėjiškom sąlygom galima susikonstruoti. Lengviausias variantas- panaudoti FPGA kūrybinę plokštę (dev board). Plokštes mes kaip ir turim, o štai softas ir FPGA source radom internete. Taip GPL licenzijos pagrindu padarytas projektėlis iš http://www.sump.org/projects/analyzer/ .

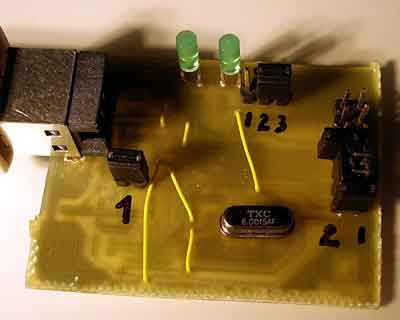

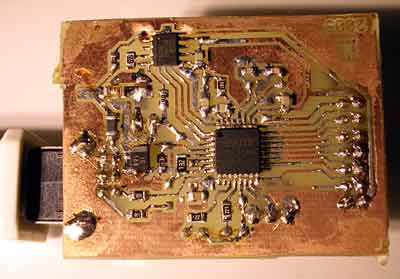

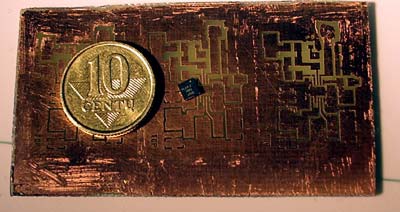

Samplinimo (nuskaitymo) dažnis iki 100MHz, naudojama statinė atmintis kuri nėra didelė. Projektas skirtas Altera DE2 plokštei (o ji brangi net ir su studentiška licenzija), todėl teko pakeisti kelis failiukus, kad veiktu su paprasetesne Cyclone dev board. Taipogi teko atsisakyti standartinės COM jungties kuri yra ant plokštės, nes mano kompo vienintelė COM jungtis užimta planšetės. Pasinaudojau savo gamybos USB-COM adapteriu kuris puikiausiai susidraugavo su pridėta programa.

Pirmas gėris kurį prijungiau prie loginio analizatoriaus tai MP3/MP4 grotuvėlis ZicPlay. Mane domina jo ekranukas, kiek suprantu tai kontroleriukas su atmintim, jis jungiasi su aparačiuku tik keliolika laidų.

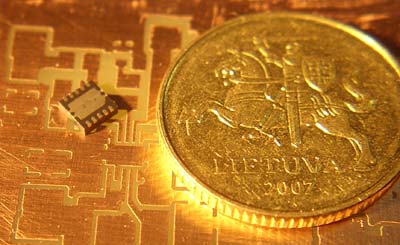

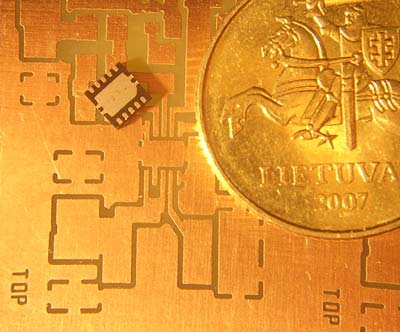

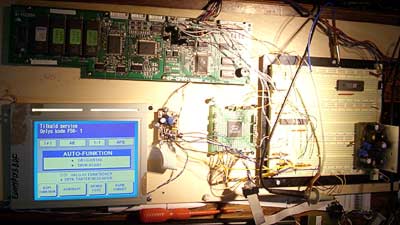

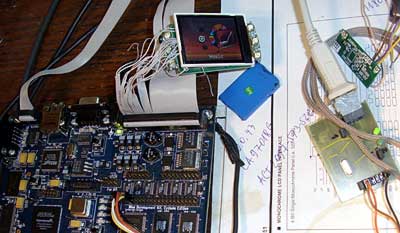

Nuotraukoje matosi Nios dev board su Cyclone EP1C20F400C7 (nors išnaudojama mažytė šio monstro dalis), per IDE ATA60/100 (80 laidininkų) kabelį pajungtas grotuvėlis. Beja, IDE kabelio pinoutas pilnai sutampa su dev board lizdu, visi žemės laidai atitinka kabelio standartą.

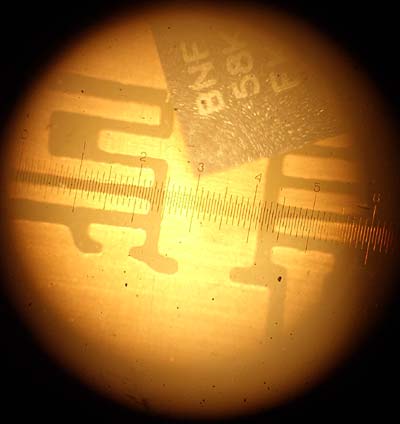

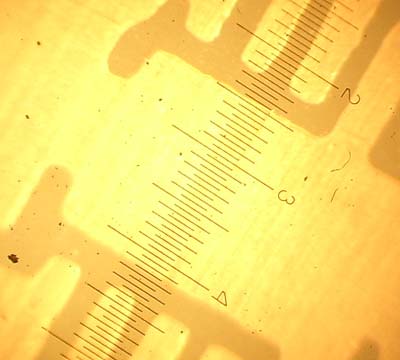

Šiose diagramose “pagautas” aparačiuko įjungimas. Grotuvėlis inicializuoja LCD ekraniuką ir jame nupaišo smėlio laikrodžio vaizdelį. Aišku šioje iliustracijoje matosi tik dalis viso vaizdelio. Samplinimo dažnis 5MHz, vaizdelis sumažintas kad gražiau atrodytu. Realiai matosi daugiau informacijos.

Mano modifikuotas FPGA source code (Quartus 7.1 versija, quartus archyvas, .qar failas). Įėjimas pajungtas prie dev board 5V tolerant jungties, USB-RS232 pajungta per 3.3V tolerant jungties. COM greitis “hardwired” FPGA konfiguracijoje. Šiaip adaptacijai reikia redaguoti tik “top” failą, visi kiti failai originalūs:Quartus archive