Jau kiek rašiau apie DEC DC J-11 procesorių. Jis kaip ir beveik veikia, bet kartu ir neveikia. Matyt nukentėjo ir mechaniškai (žiauriai pabrauktas viršus), ir elektriškai (niekas neatmeta to fakto, kad jis jau buvo blogas). O ir amžius elektronikai gana solidus.

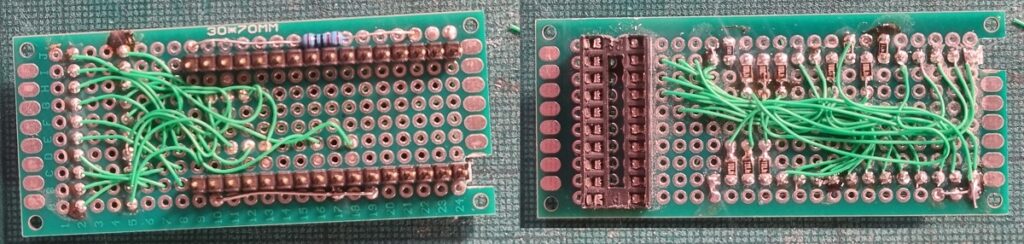

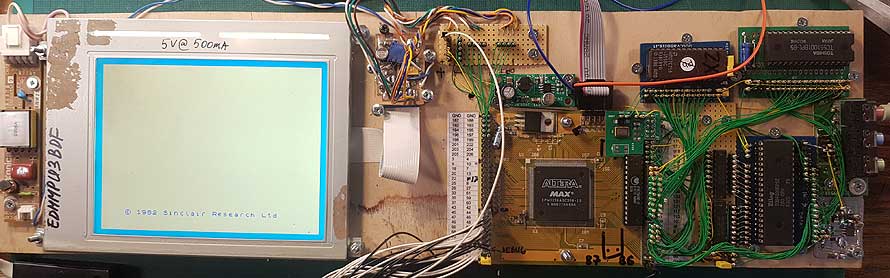

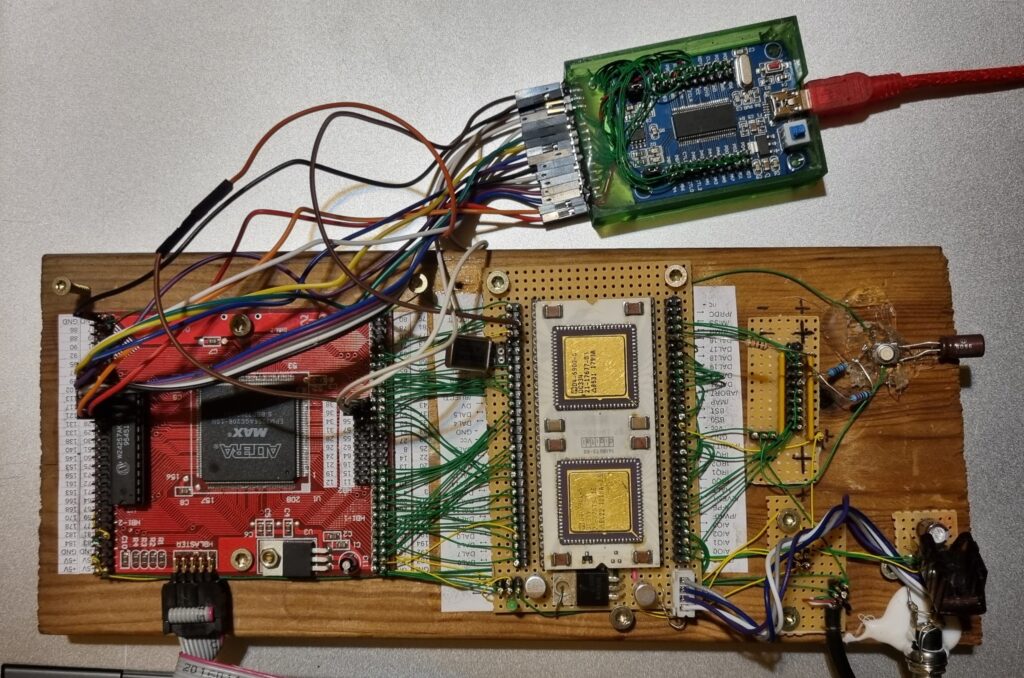

Čia mano eksperimentinė plokštė. Alteros CPLD sukonstravau šiokį tokį CPU “aprišimą” ir teoriškai jis turėjo paleisti mano mikro programą ar pasileisti į amžiną “NOP” ciklą. Tačiau procesorius pyktybiškai daro savo darbą ir iššoka į debug konsolę – ODT. Kas tai yr? Ogi tai monitoriaus “programa” leidžianti serial terminalo pagalba redaguoti atmintį, paleisti programas ir ką nors dar. Toks daiGtas kaip WozMon pas Apple 1 kompiuterį. Tik čia ne softas, o pačio CPU silikone, mikrokode parašytas softas. Kad jis veiktu nereikia nei atminties, nei kokio ROM. Reikia tik specifinės UART mikroschemos ir kelių mikroschemų. Į debug režimą galima papulti kai lūžta procesorius, HALT komanda arba “blinken lights” mygtukais.

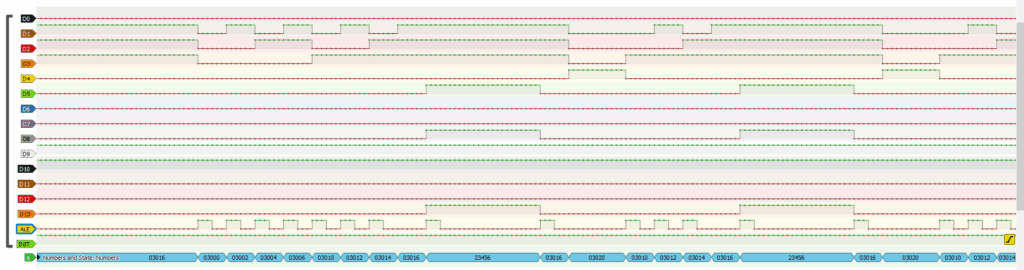

Pas mane nėra nei blinkenlights, nei UART konsolės. Todėl teko panaudoti logini analizatorių. Gaunasi maždaug taip:

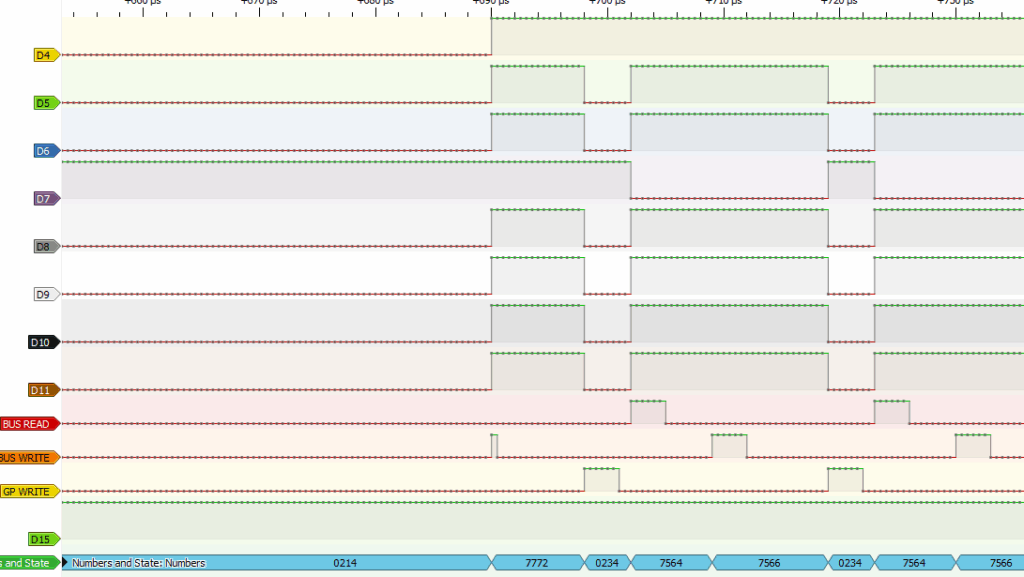

Tie skaičiukai “7772”, “7564”, “7566” tai oktaliniai gabalai adreso. Tikri adresai: o17777772, Peripheral Interrupt Request Register; o177564; Console send status (aka TPS); o177566; Console send buffer (aka TPB).

Tai čia procikas uždraudžia pertraukimus, pasitikrina ar galima siųsti simbolį ir išsiunčia simbolį per terminalą. Duomenis irgi galima pasitikrinti- ten nusipaišo “command promptas”. Tačiau aš norėjau kito režimo. Vadinasi arba nenuskaitė blinken lights, arba susihaliucionavo HALT koja arba lūžo procesorius.

Tačiau pastebėjau, kad režimas kinta nuo “taktilinio” debuginimo- priklausomai kur priglaustas pirščiukas, CPU režimai buvo kitokie. Nepadėjo net ir procesoriaus litavimas (kad ir kaip tai keistai skamba). Vistiek sistema nestabili. Kas baisiausia- problemos priklauso nuo A17… A22 kojų kurios yra …. tik išėjimai. Priklausomai ar tas kojas patempi į pliusą ar žemę. Nebent CPU manualas meluoja.

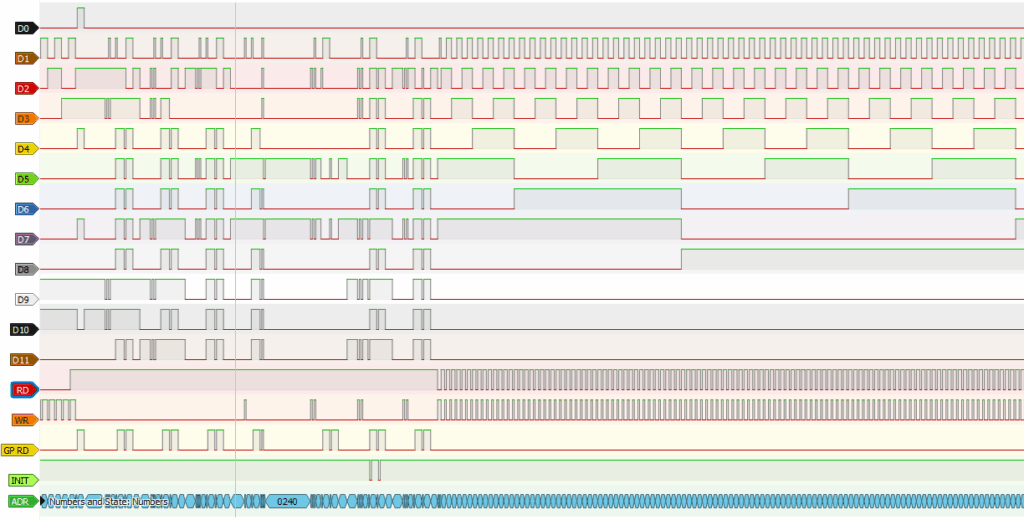

O čia kas kažkelintą kartą pasirodo kažkas įdomiau. Kogero taip veikia mano programa, kuri pabėga iš savo ciklo ir užsišoka ant NOP komandos. Ko pasekoje CPU adresas didėja ir tas labai gerai matosi ant dekoduotos (pas šiuos CPU adresas ir data yra multipleksuojamos per tas pačias kojas) adresų šynos. Čia 16 bitų procesorius ir jo NOP komanda yra 2 baitų ilgio. Todėl A0 (čia D0) nesikeičia. Keistokai atrodo WR lygis (beja, pas šį prociką nėra nei RD nei WR kojyčių. Čia irgi reikia dekoduoti). Bet šis režimas nestabiliai pasileidžia. Nu nėra mano procesorius stabilus.

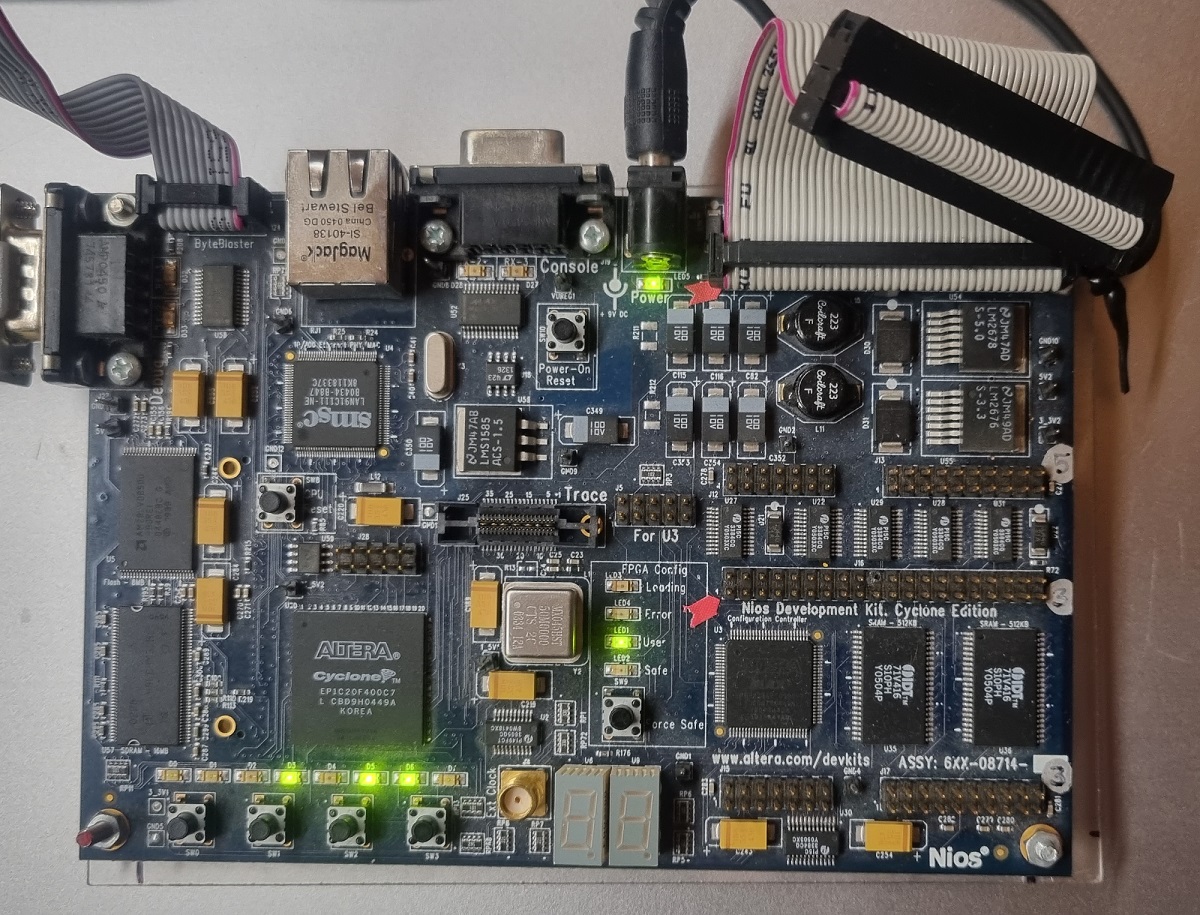

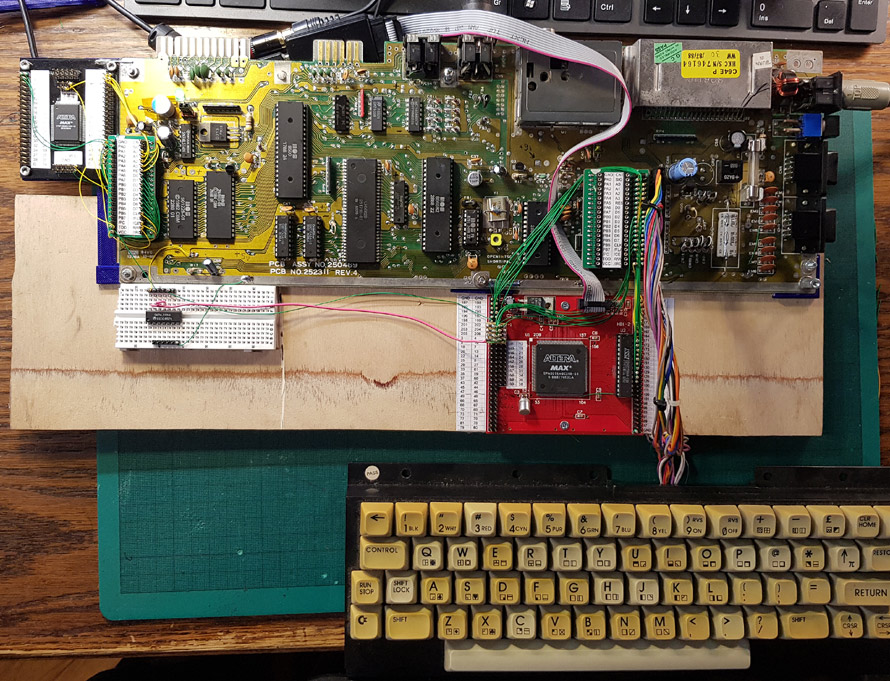

Ko pasekoje supsichavau ir nusipirkai eBay DC J11 (PDP 11/72) procesoriaus plokštę (tipo veikiančia) su būtent tokiu pat CPU. (minus 155 pinigai) ir kiek vėliau Q-Bus atminties plokštę (minus 75 pinigai)… Dar negavau.

Galvoju šiandien, kaip aš sujungsiu tas plokštes- aš gi Q-Bus backplane neturiu. Nueinu apie 16:00 į elektronikos sandėlį ir žiūrau… bl… panašu, kad guli gal ir PDP11 backpleinas. Pakėliau- surudijęs, sulankstytas, kažkoks ne PDP. Bet kištukų kiekis atitinka. Pasidėjau į slaptavietę.

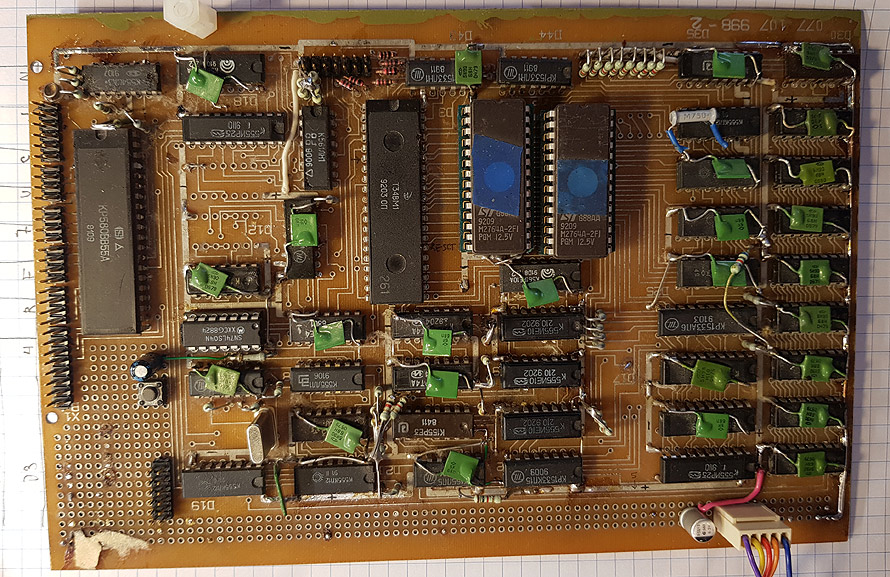

Žiūrau sau į tą kalną plokščių, jei yra backpleinas, tai gal kokia plokštelė atsiras. Radau kažkokia, analoginę lyg ir panaši, bet auksiniai kontaktai nukirpti. Dar pakuičiau ir net širdis sustojo. Va:

Tai silpnesio modelio PDP-11/23 procesoriaus plokštė su F-11 čipsetu. 18 bitų adresacija, be MMU (vadinasi mažai RAM), be FPU. Bet ALU dalis lygtai yra. Buvo baisi, išploviau su muilu, distiliuotu vandeniu ir izopropilo alkoholiu.

Ir baigėsi darbo valandos. Reikės rytoj kažkaip įsiprašyti ir kaulyti, kad leistu man rankutėmis perrinkti gal toną beviltiškų PCB. Gal netyčia rasiu ir kitas dalis, tinka net ir be auksinių kontaktų. Man labai reikėtu ODT ir ROM. Aišku ir koks nors RAM nepamaišytu. Aš panikuoju, todėl ir rašau. Nes bet kurią savaitės dieną gali išvežti viską sunaikinimui.

Po keletos valandų pisimosi

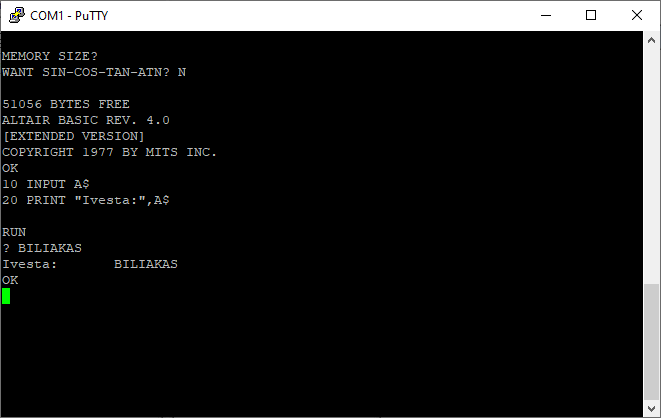

Naujas softas:

3000: 012700 MOV #1,R0 ; R0 = 1

3002: 000001

3004: 012701 MOV #1234,R1 ; R1 = 1234 (octal)

3006: 001234

3010: 005200 L0: INC R0 ; increment R0

3012: 010011 MOV R0,(R1) ; store R0 into memory at [1234]

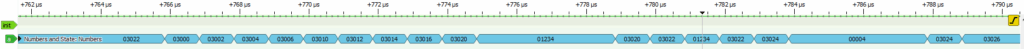

3014: 000775 BR L0 ; branch back to 3010Dabar lygtai ir veikia jei žiūrėti į loginį analizatorių. Dabar žiūrom į DAL kojas, kur ir data ar adresas multiplexinti.

3000 tai adresas, poto eina 2700. Tai 12700 galiukas. Ir kur didelis tarpas, tai duomenų “0002” rašymas į adresą “1234”.

Jei norit, pulseview failas. Kažkokie gliukai prieš paleidžiant programą ir gana įdomiai veikia tas pipeline skaitymas (ar kaip ji ten) ir viskas iš 1983 metų. Sekantis etapas- RAM ir ROM. Bet reikia perkilnoti toną PCB. Gal dar ką nors rasiu.

2025.12.16

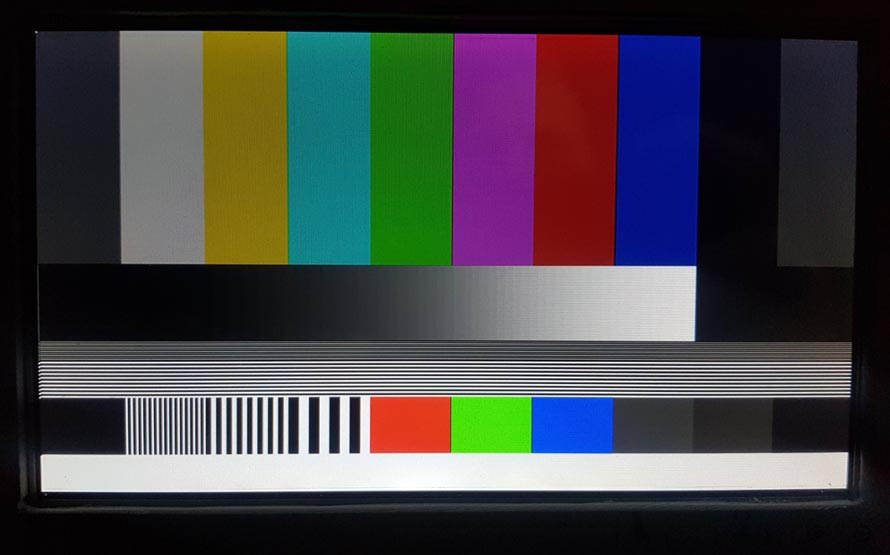

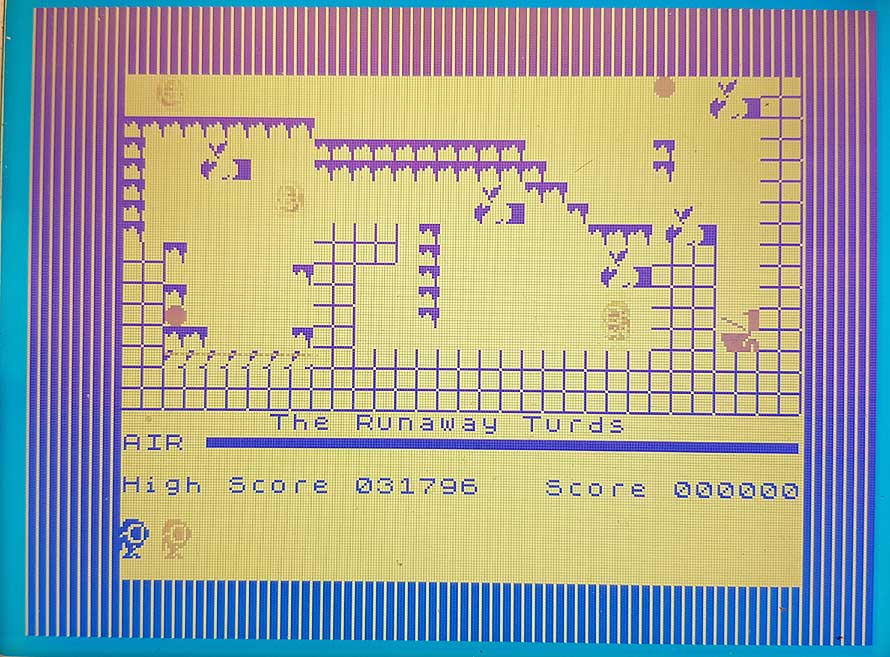

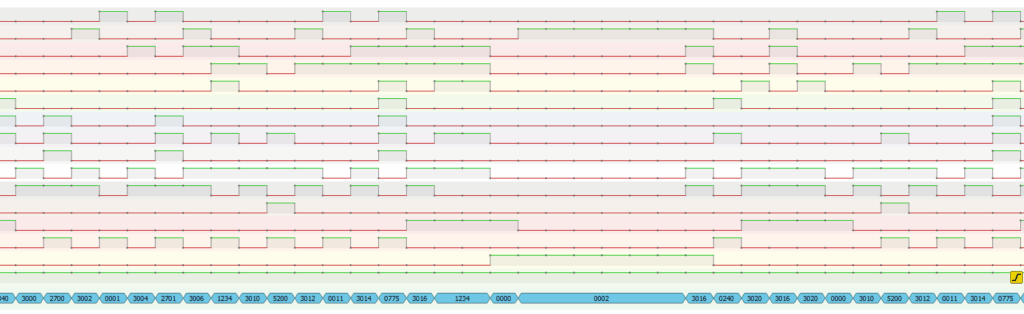

padirbėjau biški su adresų išrinkimu:

Čia boot, ir tas pats programos ciklas, tik dabar rašo į kiek kitokį adresą. Kodėl vaidenasi 3016 aš nežinau. Procesorius kaip ir veikia. Jei bandai rašyti “word” į nelyginį adresą įvyksta klaida ir procesorius šoka į kažkokį TRAP adresą, ten randa mano “NOP” ir pasileidžia adresų skaitiklis, kol persisuka adresai ir vėl papuola mano programa. Todėl ir pasidaro tas cikliškumas.

2025.12.17

Pagaliau padariau rašymą į netikrą “RAM”. Kadangi rašiau word, tai reikėjo pataisyti softą- negalima rašyti 16 bitų į nelyginį adresą. Procesorius trapinasi.

naujos “rimtos” programos source code:

000000 012700 000002 MOV #2,R0 ; R0 = 2

000004 012701 001234 MOV #1234,R1 ; R1 = 1234 (octal)

000010 005200 L0: INC R0 ; increment R0

000012 005200 INC R0 ; nes negalima nelyginių

000014 010011 MOV R0,(R1) ; store R0 into memory at [1234]

000016 011102 MOV (R1),R2 ; get from [1234] to R2

000020 010012 MOV R0,(R2) ; store R0 into memory at [R2]

000022 000772 BR L0 ; branch back to L0:

Pakeliui pagaliau pasileidau PDP makro asemblerį windows 10 aplinkoje.